US010598764B2

### (12) United States Patent

Josefsberg et al.

# (54) RADAR TARGET DETECTION AND IMAGING SYSTEM FOR AUTONOMOUS VEHICLES WITH ULTRA-LOW PHASE NOISE FREQUENCY SYNTHESIZER

(71) Applicants: **Yekutiel Josefsberg**, Netanya (IL); **Tal Lavian**, Sunnyvale, CA (US)

(72) Inventors: **Yekutiel Josefsberg**, Netanya (IL); **Tal Lavian**, Sunnyvale, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 261 days.

(21) Appl. No.: 15/797,372

(22) Filed: Oct. 30, 2017

#### (65) Prior Publication Data

US 2019/0128998 A1 May 2, 2019

(51) Int. Cl.

G01S 7/03 (2006.01)

H03L 7/23 (2006.01)

G01S 13/89 (2006.01)

G01S 13/93 (2006.01)

G01S 13/93 (2006.01)

G01S 13/931 (2020.01)

G01S 13/00 (2006.01)

(52) U.S. Cl.

#### (58) Field of Classification Search

None

See application file for complete search history.

#### (10) Patent No.: US 10,598,764 B2

(45) **Date of Patent:** Mar. 24, 2020

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 4,543,577 A * | 9/1985 | Tachibana G01S 13/931    |

|---------------|--------|--------------------------|

|               |        | 340/901                  |

| 5,146,186 A * | 9/1992 | Vella H03L 7/185         |

| 5 150 078 A * | 9/1992 | 331/11<br>Yang H03L 7/23 |

| 3,130,070 11  | 3/1332 | 331/2                    |

| 5,281,949 A * | 1/1994 | Durley G01S 13/931       |

|               |        | 180/167                  |

(Continued)

Primary Examiner — Bernarr E Gregory

#### (57) ABSTRACT

A target detection and imaging system, comprising a RADAR unit and at least one ultra-low phase noise frequency synthesizer, is provided. The target detecting, and imaging system can assist other sensors such as LiDAR, camera to further detect and investigate objects on the road from distance. RADAR unit configured for detecting the presence and characteristics of one or more objects in various directions. The RADAR unit may include a transmitter for transmitting at least one radio signal; and a receiver for receiving the at least one radio signal returned from the one or more objects. signals. The ultra-low phase noise frequency synthesizer may utilize dual loop design comprising one main PLL and one sampling PLL, where the main PLL might include a DDS or Fractional-N PLL plus a variable divider, or the synthesizer may utilize a sampling PLL only, to reduce phase noise from the returned radio signal. This proposed system overcomes deficiencies of current generation state of the art RADAR Systems by providing much lower level of phase noise which would result in improved performance of the RADAR system in terms of target detection, characterization etc.

#### 20 Claims, 53 Drawing Sheets

## US 10,598,764 B2 Page 2

| (56) References Cited |                                        | 8,704,562 B2*       | 4/2014  | Nicholls H03L 7/185    |

|-----------------------|----------------------------------------|---------------------|---------|------------------------|

| II S DA               | TENT DOCUMENTS                         | 9.052.393 B2*       | 6/2015  | Kriel G01S 13/867      |

| 0.5.1A                | MENT DOCUMENTS                         | 9,162,643 B2*       | 10/2015 | Pech                   |

| 5,343,168 A * 8       | 8/1994 Guthrie H03L 7/185              | 9,239,380 B2 *      | 1/2016  | Hegemann G01S 13/931   |

| 3,5 13,100 71         | 331/16                                 | 9,705,511 B2*       | 7/2017  | Josefsberg H03L 7/185  |

| 5.493.269 A * 2       | 2/1996 Durley G01S 13/931              | 9,831,881 B2*       | 11/2017 | Josefsberg H03L 7/185  |

| -,,                   | 180/167                                | 10,205,457 B1*      | 2/2019  | Josefsberg G01S 7/032  |

| 6,035,053 A * 3       | 3/2000 Yoshioka G01S 13/931            | 10,302,741 B2 *     | 5/2019  | Ahmad G01S 13/931      |

|                       | 340/435                                | 10,404,261 B1*      | 9/2019  | Josefsberg G01S 13/931 |

| 6,037,860 A * 3       | 3/2000 Zander G01S 13/931              | 2007/0013497 A1*    | 1/2007  | Watanabe G01S 13/931   |

|                       | 307/10.1                               | 2007/0015157 111    | 1/200/  | 340/435                |

| 6,122,326 A * 9       | 9/2000 Jackson H03L 7/23               | 2009/0309665_A1*    | 12/2009 | Chenakin H03L 7/185    |

|                       | 332/127                                | 2003/0303003 111    | 12.2003 | 331/25                 |

| 6,239,660 B1 *        | 5/2001 Dekker H03L 7/185               | 2012/0303258 A1*    | 11/2012 | Pampus G01S 13/931     |

| C 420 007 D1 # - /    | 331/18                                 | 2012/0303230 111    | 11/2012 | 701/301                |

| 6,420,997 B1 * ´      | 7/2002 Cong G01S 13/931                | 2013/0342277 A1*    | 12/2013 | Roth H03L 7/185        |

| 7.012.561 B2 * 3      | 342/70<br>3/2006 Toennesen G01S 13/582 | 2013/03/122// 111   | 12.2015 | 331/18                 |

| 7,012,301 B2 · .      | 3/2000 Toennesen                       | 2014/0333467 A1*    | 11/2014 | Inomata G01S 13/867    |

| 7.053.817 B2 *        | 5/2006 Nakano G01S 13/931              |                     |         | 342/27                 |

| 7,033,017 B2          | 342/90                                 | 2016/0164528 A1*    | 6/2016  | Morton H03L 7/093      |

| 7.545.224 B2 * 0      | 6/2009 Chow H03L 7/10                  | 2010/010/020 111    | 0.2010  | 327/157                |

| .,,                   | 331/16                                 | 2017/0254882 A1*    | 9/2017  | Malik G01S 13/931      |

| 7,656,236 B2 * 2      | 2/2010 Williams H03L 7/087             | 2017/0307751 A1*    | 10/2017 | Rohani G01S 13/931     |

|                       | 331/1 R                                | 2018/0067966 A1*    | 3/2018  | Oder G01S 13/867       |

| 8,669,854 B2 * 3      | 3/2014 D'Ambrosio G01S 13/931          |                     |         | 3223 10,007            |

|                       | 340/435                                | * cited by examiner |         |                        |

FIG. 5

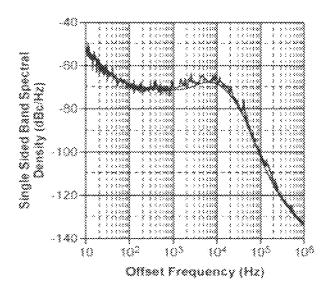

#### Measured Phase Noise

FIG. 10

-1G. 14

FIG. 13

FIG. 31 (Prior Art)

FIG. 34 (Prior Art)

FIG. 36 (Prior Art)

FIG. 40A

FIG. 40B

FIG. 41

FIG. 4

FIG. 47

FIG. 48

# RADAR TARGET DETECTION AND IMAGING SYSTEM FOR AUTONOMOUS VEHICLES WITH ULTRA-LOW PHASE NOISE FREQUENCY SYNTHESIZER

### **FIELD**

Embodiments of the present disclosure are generally related to sensors for 0autonomous vehicles (for example, Self-Driving Cars) and in particular to systems that use 10 ultra-low phase noise frequency synthesizer for RADAR Sensor Applications for autonomous vehicles.

#### BACKGROUND

Autonomous vehicles are paving way for a new mode of transportation. Autonomous vehicles require minimum or no intervention from vehicle's driver. Generally, some autonomous vehicles need only an initial input from the driver, whereas some other designs of the autonomous vehicles are 20 continuously under control of the driver. There are some autonomous vehicles that can be remotely controlled. For example, automatic parking in vehicles is an example of the autonomous vehicle in operation.

Autonomous vehicles face dynamic environment that is 25 the environment keeps changing every time. The autonomous vehicles need to keep a track of lane markings, road edges, track road curves, varying surfaces that may be include flat surfaces, winding roads, hilly roads etc. Alongside, the autonomous vehicles also need to keep a check on 30 objects that are both stationary or mobile like a tree or a human or an animal. Hence, the autonomous vehicles need to capture a huge amount of information that keeps on changing every time.

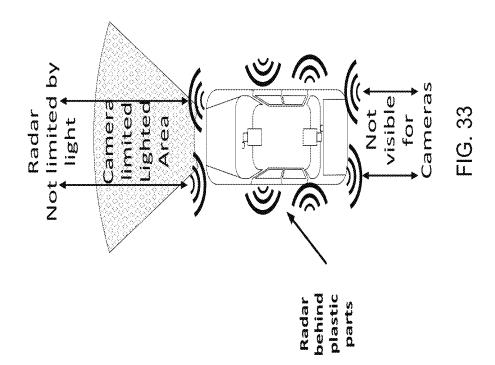

Therefore, to overcome and meet these challenges, 35 autonomous vehicles are provided with various set of sensors. These sensors help the vehicle to gather all around information and help in increasing the degree of autonomy of the vehicle. The various types of sensors currently being used in autonomous vehicles are LiDAR sensors, Ultrasonic 40 sensors, Image sensors, Global Positioning System (GPS) sensors, Inertial Measurement unit (IMU) sensors, dead reckoning sensors, Microbolo sensors, Speed sensors, Steering-angle sensors, Rotational speed sensors, and RADAR sensors. Two of the most used sensors are LiDAR and 45 RADAR sensors.

LiDAR sensors: LiDAR is a device that maps objects in 3-dimensional by bouncing laser beams off its real-world surroundings. LiDAR in automotive systems typically use 905 nm wavelength that can provide up to 200 m range in 50 restricted FOVs (field of views). These sensors scan the environment, around the vehicle, with a non-visible laser beam. LIDAR sensor continually fires off beams of laser light, and then measures how long it takes for the light to return to the sensor. The laser beam generated in of low 55 intensity and non-harmful. The beam visualizes objects and measures ranges to create a 3D image of the vehicle's surrounding environment. LiDAR sensors are very accurate and can gather information to even up to very close distances around the vehicle. However, LiDAR sensors are generally 60 bulky, complex in design and expensive to use. The costs can go up to \$100,000. LiDAR may also require complex computing of the data collected that also adds to the costs. Also, LiDARs can only capture data up to a distance of 200

It is to be noted that LiDAR requires optical filters to remove sensitivity to ambient light and to prevent spoofing 2

from other LiDARs. Also, the laser technology used has to be "eye-safe". Recently mechanical scanning LiDAR, that physically rotate the laser and receiver assembly to collect data over an area that spans up to 360° have been replaced with Solid State LiDAR (SSL) that have no moving parts and are therefore more reliable especially in an automotive environment for long term reliability. However, SSLs currently have lower field-of-view (FOV) coverage.

RADAR sensors: RADAR sensors basically send out electro-magnetic waves. When these waves hit an obstacle, they get reflected. Thus, revealing how far away an object is and how fast is it approaching.

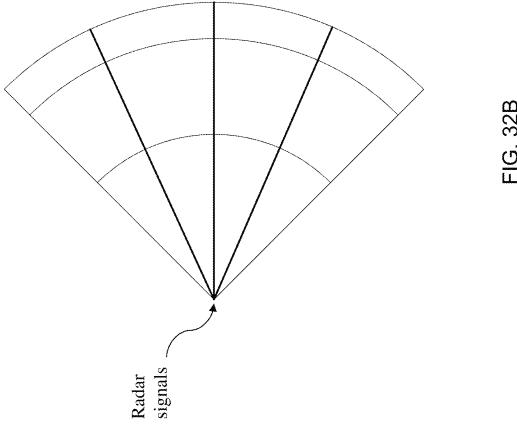

Automotive RADARs can be categorized into three types: long range RADARs, medium range RADARs and shortrange RADARs. Long range RADARs are used for measuring the distance to and speed of other vehicles. Medium range RADARs are used for detecting objects within a wider field of view e.g. for cross traffic alert systems. Short range RADARs are used for sensing in the vicinity of the car, e.g. for parking aid or obstacle detection. Depending on the application, RADAR requirements differ. Short range applications require a steerable antenna with a large scanning angle, creating a wide field of view. Long range applications on the other hand, require more directive antennas that provide a higher resolution within a more limited scanning range. Two different frequency bands are mainly used for automotive RADARs: the 24 GHz band and the 77 GHz band. The 77 GHz band offers higher performance, but it is also more challenging to implement since for example losses are much higher at these frequencies. The 24 GHz RADARs are easier to develop but are larger in size, making it difficult to integrate them in a vehicle. RADARs operating at 24 GHz require around three times larger antennas than RADARs operating at 77 GHz, to achieve the same performance. A 77 GHz RADAR would thus be much smaller resulting in easier integration and lower cost. Moving to higher frequencies enables RADARs with a better resolution. However, a major challenge posed is to develop steerable antennas for 77 GHz RADARs with high enough performance at a reasonable cost.

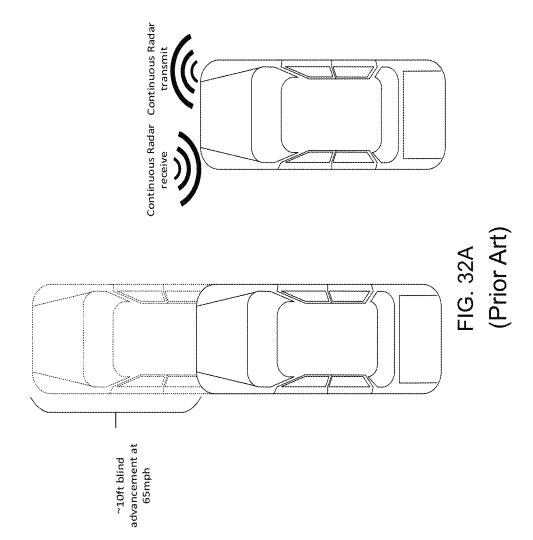

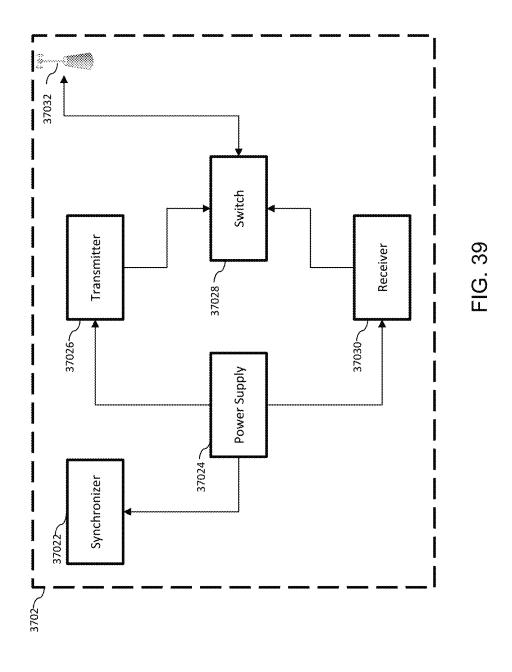

Automotive RADAR systems use a pulse-Doppler approach, where the transmitter operates for a short period, known as the pulse repetition interval (PRI), then the system switches to receive mode until the next transmit pulse. As the RADAR returns, the reflections are processed coherently to extract range and relative motion of detected objects. Another approach is to use continuous wave frequency modulation (CWFM). This approach uses a continuous carrier frequency that varies over time with a receiver on constantly. To prevent the transmit signal from leaking into the receiver, separate transmit and receive antennas are used.

RADAR sensors are low priced and provide as excellent sensors. RADARs also cost very less and may be procured within \$150. These sensors work extremely accurately in bad weather conditions like fog, snow, dirt, etc. RADAR sensors use extremely simple circuitry and thus are smaller in size that makes them easy to be manufactured, installed and used. However, one of the major drawbacks of the RADAR sensors is that they give confused results when multiple objects are within the range. They are not able to filter noise in such situations. Existing RADARs do not offer the necessary resolution to distinguish objects with sufficient reliability. One of the main problems faced is the separation of small and large objects that travel at the same distance and velocity in adjacent lanes, e.g. a motorcycle driving in the lane next to a truck.

Major factors affecting RADAR performance are: Transmitter Power and Antenna Size:

The maximum range of a RADAR system depends in large part on the average power of its transmitter and the physical size of its antenna. This is also called the poweraperture product. There are practical limits to each of these. Receiver Noise:

The sensitivity of a RADAR receiver is determined by the unavoidable noise that appears at its input. At microwave RADAR frequencies, the noise that limits detectability is usually generated by the receiver itself (i.e., by the random motion of electrons at the input of the receiver) rather than by external noise that enters the receiver via the antenna. Target Size:

The size of a target as "seen" by RADAR is not always related to physical size of the object. The measure of the target size as observed by RADAR is called RADAR cross section and is determined in units of area (square metres). It is possible for two targets with the same physical cross- 20 sectional area to differ considerably in RADAR size, or RADAR cross section. For example, a flat plate 1 square metre in area will produce a RADAR cross section of about 1,000 square metres at a frequency of 3 GHz when viewed perpendicular to the surface. A cone-sphere (an object 25 resembling an ice-cream cone) when viewed in the direction of the cone rather than the sphere could have a RADAR cross section of about 0.001 square metre even though its projected area is also 1 square metre. Hence, this may cause calculation mistakes and may give wrong estimation of the objects identified.

Clutter:

Echoes form environment factors like land, rain, birds and other similar objects may cause nuisance to detect objects. Clutter makes it difficult to identify objects and their properties to a considerable extent.

Interference:

Signals from nearby RADARs and other transmitters can be strong enough to enter a RADAR receiver and produce 40 spurious responses. Interference is not as easily ignored by automatic detection and tracking systems. Hence, interference may further add to noise to the RADAR signals. Comparison Between LiDAR and RADAR

As compared to LiDAR sensors, RADAR sensors provide 45 more robust information to the vehicles. LiDAR sensors are generally mounted on top of the vehicle and are mechanically rotated to gather surrounding information. This rotational movement is prone to dysfunction. Whereas in case of RADAR, as they are solid state and have no moving parts 50 hence have minimal rate of failures.

Also, LiDAR sensors produce pulsed laser beams and hence are able to gather information only when the pulsed beam is generating the laser beams. RADAR sensors can generate continuous beams and hence provide continuous 55 information.

Also, LiDAR sensors generate enormous and complex data for which complex computational modules are required to be used. For example, some types of LIDAR systems generate amounts of 1-Gb/s data that require substantial 60 amount of computation by strong computers to process such high mount of data. In some cases, these massive computations require additional computation and correlation of information from other sensors and sources of information. This increases cost heads for vehicle manufacturers. 65 Whereas, RADAR sensors only generate small fractions of data that is easy to compute.

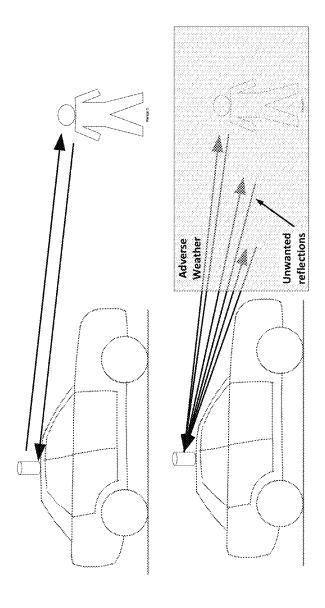

4

LiDAR sensors are also sensitive to adverse weather conditions such as rain, fog, and snow while RADAR sensors are not prone to any weather conditions.

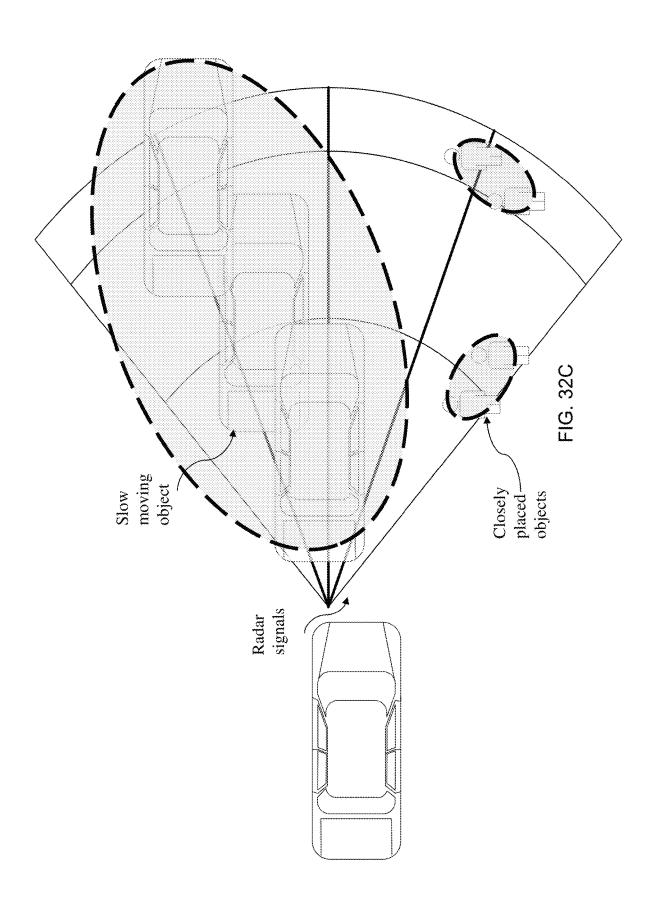

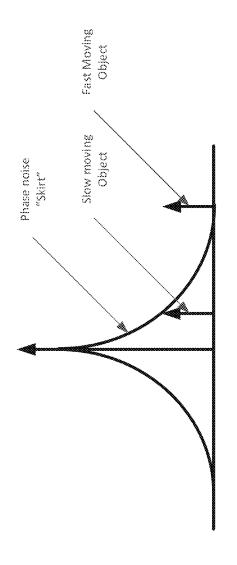

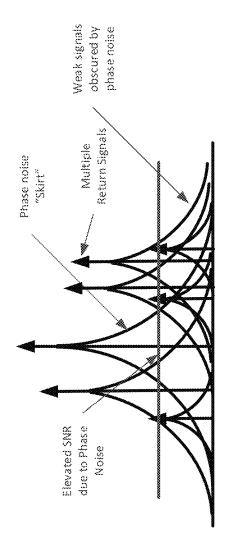

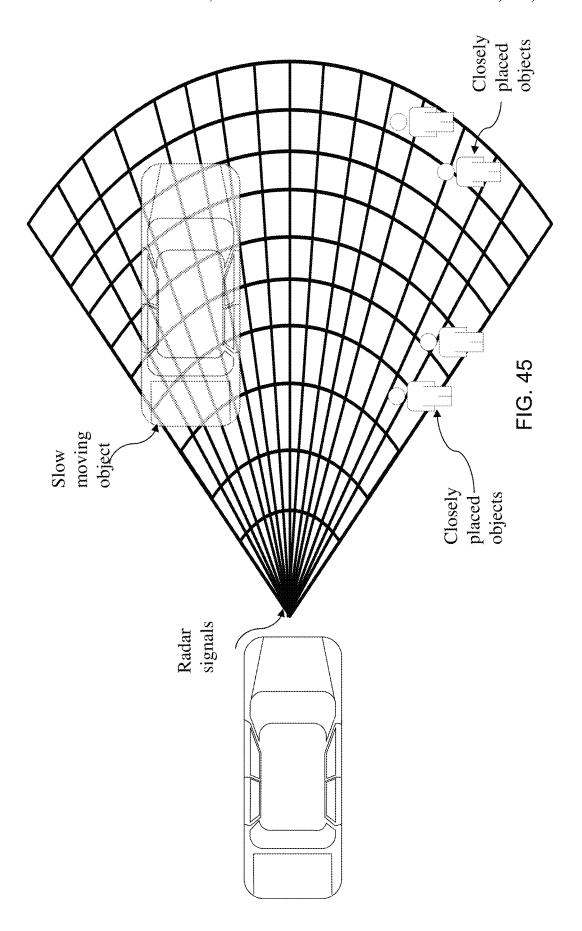

However, RADAR sensors are challenged when dealing with slow moving objects such as cars, bicycles and pedestrians. Furthermore, these traditional RADAR systems, whether using a modulated or non-modulated signal, have difficulties identifying objects that are very close to each other since one of them will be obscured by the phase noise of the system. Also, the drawback of existing RADAR sensors is the impact on their accuracy due to the phase noise of its frequency source, the synthesizer. RADAR sensors are not able to relay size and shape of objects as accurately as LiDAR. RADAR sensors are not a stand-alone solution. They are accompanied by ultrasonic sensors or cameras.

Therefore, there is a need for an enhanced RADAR system capable of implementing artificial intelligence for helping in making informed decisions based on surrounding information. Furthermore, the system should be capable to overcome the shortcomings of the existing systems and technologies.

#### **SUMMARY**

Some of the Benefits of the Invention: The present invention emphasizes that by incorporating the ultra-low phase noise synthesizer in existing RADAR system, the performance of the RADAR system will be improved substantially in terms of target detection accuracy and resolution and because of this it can become the dominant sensor for the handling of autonomous cars. Herein, the Synthesizer drastically reduces the phase noise of RADAR signals so that such RADAR sensor will be able to replace current sensor systems at very low cost and with reliability at all lighting and adverse weather conditions.

A system that utilizes an ultra-low phase noise synthesizer will be able to provide data to a processor that can determine the electromagnetic characteristics of an object with sufficient accuracy so that the system is able to determine if the object is a living object such as a human being or an animal or if it is inanimate. It will also be able to provide data that is accurate enough to differentiate between the material objects are made of such as differentiating between wood and stone for example. As an example, the data generated by the RADAR system could be used to identify and verify the presence of a human on the sidewalk about to cross the street or a bicycle rider at the side of the road.

Further as a derivative of the capability to determine the material an object is made of combined with the electromagnetic waves capability to penetrate through many materials an object detection and imaging system utilizing an ultra-low phase noise synthesizer will provide data that will enable a processing unit (such as a specialized processor of the object detection and imaging system) to find objects that are visually obscured by another object and determine the material of the obscured and obscuring object. Thus, the system may be able to find a human behind a billboard/bus station advertisement or wildlife behind a bush or determine that these are only 2 bushes (or non animated objects) one behind the other.

Additionally, a RADAR system that utilizes an ultra-low phase noise synthesizer may be used as an imaging RADAR that can discover silhouettes and create a true 3-dimensional map of the surroundings of the vehicle including the mapping of object that are not visible with light. Such a RADAR System would beneficially utilize SAR technology, Interferometry and Polarimetry to define the exact characteristics of

and objects backscatter such as, but not limited to, Surface roughness, Geometric structure, Orientation and more. Further, an ultra-low phase noise RADAR system enables the determination of electrical characteristic such as, but not limited to, Dielectric constant, Moisture content, Conduc- 5 tivity and more.

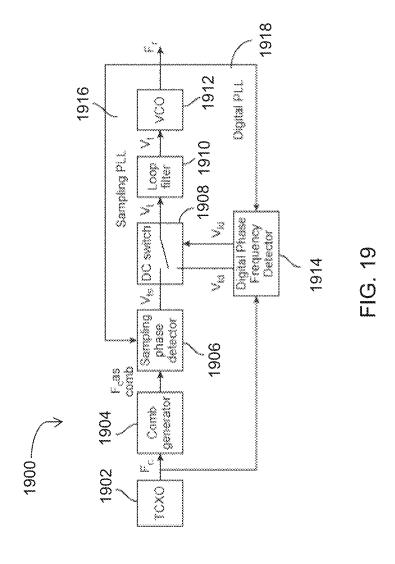

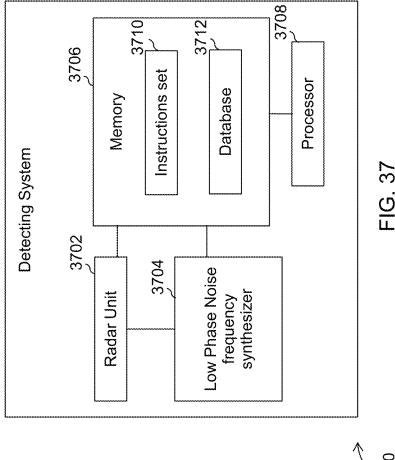

According to an embodiment of the present disclosure an object detection and imaging system for autonomous vehicles is provided, The object detection and imaging system may include a RADAR unit coupled to at least one 10 ultra-low phase noise frequency synthesizer, configured for detecting the presence of one or more objects in one or more directions, the RADAR unit comprising: a transmitter for transmitting at least one radio signal; and a receiver for receiving at least one radio signal returned from one or more 15 objects/targets. Further, the object detection and imaging system may include the at least one ultra-low phase noise frequency synthesizer that may be utilized in conjunction with the RADAR unit, for refining both the transmitted and the received signals, and thus determining the phase noise 20 and maintaining the quality of the transmitted and the received radio signals, wherein the at least one ultra-low phase noise frequency synthesizer comprises: (i) at least one clocking device configured to generate at least one first one sampling Phase Locked Loop (PLL), wherein the at least one sampling PLL comprises: (a) at least one sampling phase detector configured to receive the at least one first clock signal and a single reference frequency to generate at least one first analog control voltage; and (b) at least one 30 reference Voltage Controlled Oscillator (VCO) configured to receive the at least one analog control voltage to generate the single reference frequency; and (c) a Digital Phase/Frequency detector configured to receive the at least one first clock signal and a single reference frequency to generate at 35 least a second analog control voltage; and (d) a two-way DC switch in communication with the Digital Phase/Frequency detector and the sampling phase detector; (iii) at least one first fixed frequency divider configured to receive the at least one reference frequency and to divide the at least one 40 reference frequency by a first predefined factor to generate at least one clock signal for at least one high frequency low phase noise Direct Digital Synthesizer (DDS) clock signal; (iv) at least one high frequency low phase noise DDS configured to receive the at least one DDS clock signal and 45 to generate at least one second clock signal of at least one second clock frequency; and (v) at least one main Phase Locked Loop (PLL).

Hereinabove, the main PLL may include: (a) at least one high frequency Digital Phase/Frequency detector configured 50 to receive and compare the at least one second clock frequency and at least one feedback frequency to generate at least one second analog control voltage and at least one digital control voltage; (b) at least one main VCO configured to receive the at least one first analog control voltage or the 55 at least one second analog control voltage and generate at least one output signal of at least one output frequency, wherein the at least one digital control voltage controls which of the at least one first analog control voltage or the at least one second analog control voltage is received by the 60 at least one main VCO; (c) at least one down convert mixer configured to mix the at least one output frequency and the reference frequency to generate at least one intermediate frequency; and (d) at least one second fixed frequency divider configured to receive and divide the at least one 65 intermediate frequency by a second predefined factor to generate the at least one feedback frequency.

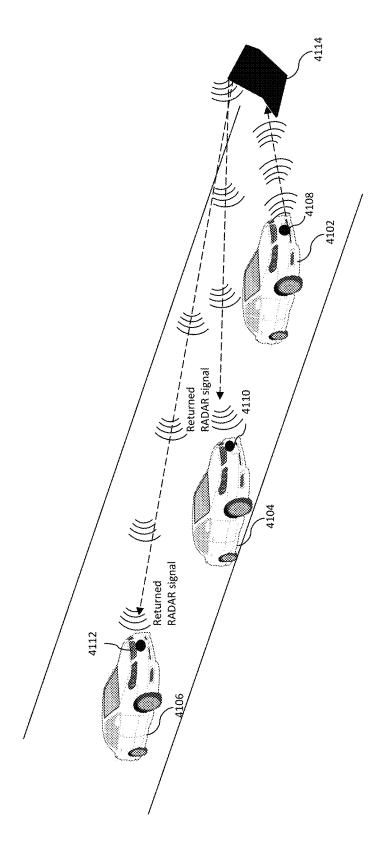

Herein, the RADAR unit or units create a 3-dimensional RADAR image using one or more RADAR sensors and/or one or more frequencies. The transmitting RADAR may be at one location of the vehicle while the receiving unit is at another location. The RADAR sensors may utilize Synthetic aperture RADAR (SAR) technology to create the 3-dimensional image. The 3-dimensional image may include information about objects that are obscured for visible light. In an embodiment, Bi-static and multi-static may also involve one vehicle transmitting while one or more other vehicles receive the return signals.

Herein, the radar unit determines a distance and a direction of each of one or more objects. Further, the radar unit determines one or more characteristics, of two close objects irrespective of size of the one or more objects. Again further, the radar unit differentiates between two or more types of the objects when one object is visually obscuring another object. Additionally, the radar unit utilizes a modulated or nonmodulated radio signal, to determine presence of a slowmoving target despite the very small Doppler frequency shift. Also, the radar unit utilizes a modulated or nonmodulated radio signal, to determine presence of a closerange target despite the very short signal travel time.

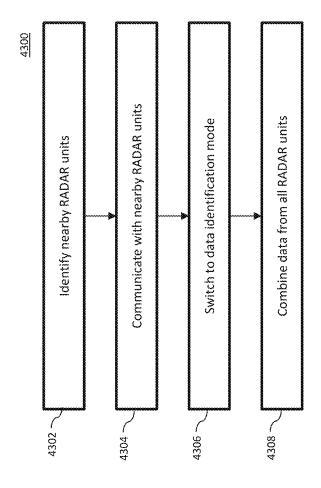

Additionally, a vehicle with RADAR imaging capabilities clock signal of at least one first clock frequency; (ii) at least 25 may create contact with other vehicles that have that same feature. The group of 2 vehicles or more will set up an identification scheme so that every vehicle will be able to detect return signals from every other vehicle and thus combine a 3-dimensional map of the surroundings for immediate autonomous driving purposes and/or mapping or any other purpose.

> The object detection and imaging system may further include at least one additional sensor system, available on the autonomous vehicle, or a database connection in conjunction with the RADAR unit. The combined object detection and imaging system may be used as real-time sensors and or as mapping device. Considering the example of the pedestrian on the sidewalk or the bicycle rider at the side of the road once the RADAR unit has detected something of interest this can be used in conjunction with other sensors, a LiDAR device for instance. In such a case the visible field for the LiDAR could be reduced to 1/100 of its usual Field Of View (FOV) and the elevation angle by another 1/10 to 1/100 of its original FOV reducing the computation needed for the LiDAR by 1/1000 to 1/10000.

> Further, the at least one ultra-low phase noise frequency synthesizer further comprises at least one fixed frequency multiplier configured to receive and multiply the at least one output signal generated by the at least one main PLL by a predefined factor to generate at least one final output signal of at least one final output frequency. The at least one ultra-low phase noise frequency synthesizer is implemented on the same electronic circuitry or on a separate electronic circuitry. Further, the ultra-low phase noise frequency synthesizer may be used to generate the up or down converting signal of the RADAR unit.

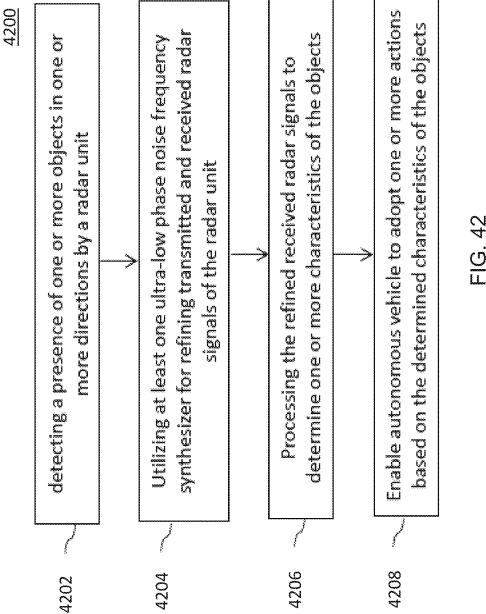

> Further, according to another embodiment of the present disclosure, a method for autonomous vehicles is disclosed. The method may include (but is not limited to): detecting a presence of one or more objects in one or more directions by a RADAR unit. Herein, the RADAR unit comprising: a transmitter for transmitting at least one radio signal to the one or more objects; and a receiver for receiving the at least one radio signal returned from the one or more objects. Further, the method may include performing, by at least one ultra-low phase noise frequency synthesizer for refining the transmitted and the received signals, and thereby determin-

ing a phase noise and maintaining quality of the transmitted and the received radio signals.

Herein, the method may further include various steps such as receiving and multiplying, by ultra-low phase noise frequency synthesizer, the at least one output signal by a 5 predefined factor to generate at least one final output signal of at least one final output frequency. Further, the method may generate the up converting or down converting signal of the RADAR unit. Furthermore, the method may determine presence of a slow-moving target despite the very small 10 Doppler frequency shift. Again further, the method may include determining presence of a close-range target despite the very short signal travel time. Additionally, the method may determine a distance and a direction of each of the one or more objects. Furthermore, the method may determine a 15 type of material an object is made up of. Also, the method may include a step of activating one or more additional sensors for operation thereof in conjunction with the RADAR unit. The method may determine characteristics of two close objects irrespective of size of the objects. Further, 20 the method may differentiate between two or more types of the objects when one object is visually obscuring another object.

According to an embodiment of the present disclosure, a system is a detection and imaging system that comprises a 25 RADAR unit, communicably coupled to at least one ultralow phase noise frequency synthesizer, is provided. The RADAR unit configured for detecting the presence of one or more objects in one or more directions. Herein, the RADAR unit comprising: a transmitter for transmitting at least one 30 radio signal; and a receiver for receiving at least one radio signal returned from one or more objects/targets. Further, the detection and imaging system may include at least one ultra-low phase noise frequency synthesizer that may be configured for refining the returning the at least one radio 35 signal to reduce phase noise therefrom.

Herein, the ultra-low phase noise frequency synthesizer is a critical part of a System, regardless of how it is implemented. The ultra-low phase noise frequency synthesizer comprises one main PLL (Phase Lock Loop) and one 40 reference sampling PLL. The main PLL comprises one high frequency DDS (Direct Digital Synthesizer), one Digital Phase Frequency Detector, one main VCO (Voltage Controlled Oscillator), one internal frequency divider, one output frequency divider or multiplier and one down convert 45 mixer. The reference sampling PLL comprises one reference clock, one sampling phase detector, one digital phase/frequency detector and one reference VCO. This embodiment provides vast and critical improvement in the overall system output phase noise. The synthesizer design is based on the 50 following technical approaches—a) using of dual loop approach to reduce frequency multiplication number, b) using of sampling PLL as the reference PLL to make its noise contribution negligible, c) using of DDS to provide high frequency input to the main PLL and d) using of high 55 frequency Digital Phase Frequency Detector in the main

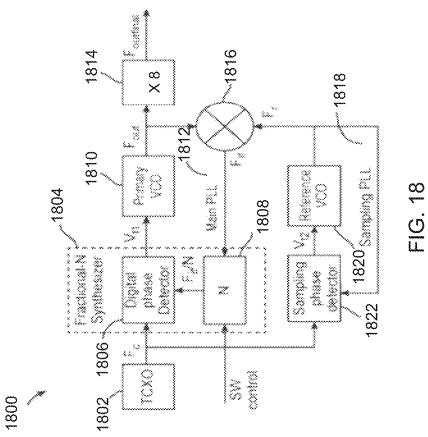

In an additional embodiment of present disclosure, The ultra-low phase noise frequency synthesizer comprises one main PLL (Phase Lock Loop) and one reference sampling 60 PLL. The main PLL further comprises one Fractional-N Synthesizer chip, one primary VCO (Voltage Controlled Oscillator) and one down convert mixer. The Fractional-N Synthesizer chip includes one Digital Phase Detector and one software controllable variable frequency divider. The 65 reference sampling PLL comprises one reference clock, one sampling phase detector, one digital phase/frequency detec-

8

tor and one reference VCO. This embodiment provides multiple improvements in system output which are based on the following technical approaches—a) using of dual loop approach to reduce frequency multiplication number, b) using of sampling PLL to make its noise contribution negligible, and c) using of a high frequency Fractional-N Synthesizer chip in the main PLL.

In an additional embodiment of present disclosure, the ultra-low phase noise frequency synthesizer comprises one sampling PLL. The sampling PLL comprises one reference clock, one sampling phase detector, one digital phase/frequency detector and one VCO.

According to an embodiment of the present disclosure a detection system comprising a RADAR unit and an ultralow phase noise frequency synthesizer is provided. The system is made up of System on Chip (SoC) module. The RADAR unit configured for detecting the presence or imaging of one or more objects in one or more directions. The RADAR unit comprising: a transmitter for transmitting at least one radio signal; and a receiver for receiving the at least one radio signal returned from the one or more objects/ targets. In an embodiment, the Transmit and receive signal frequencies might be equal. For example, if there is no Doppler effect, the signal frequencies may be equal. In an embodiment, the transmit and receive frequencies might also be different, for example in cases where the doppler effect is present. The ultra-low phase noise frequency synthesizer comprises one main PLL (Phase Lock Loop) and one reference sampling PLL. The main PLL further comprises one Fractional-N Synthesizer chip, one primary VCO (Voltage Controlled Oscillator) and one down convert mixer. The Fractional-N Synthesizer chip includes one Digital Phase Detector and one software controllable variable frequency divider. The reference sampling PLL comprises one sampling PLL, and one reference VCO. This embodiment provides multiple improvements in system output which are based on the following technical approaches—a) using of dual loop approach to reduce frequency multiplication number, b) using of sampling PLL to make its noise contribution negligible, and c) using of a high frequency Fractional-N Synthesizer chip in the main PLL.

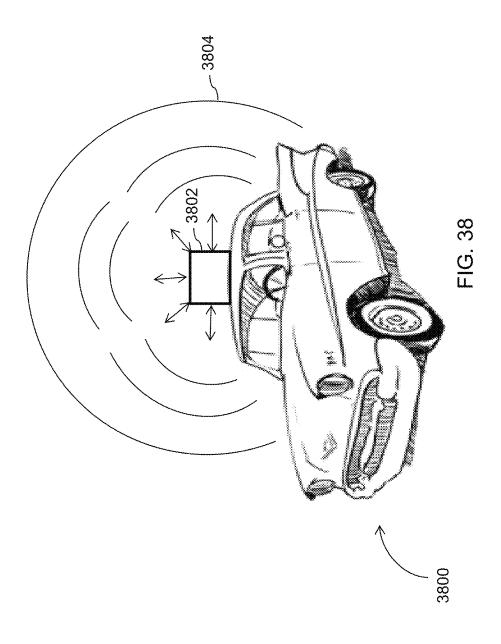

In an additional embodiment of the present disclosure, a vehicle having a detection and imaging system is disclosed. The detection and imaging system may be implemented for detecting information corresponding to one or more objects, the detection unit comprising: a RADAR unit for transmitting radio signals and further for receiving the returned radio signal(s) from one or more objects/targets; and at least one ultra-low phase noise frequency synthesizer for refining the returned signals to reduce the effect of phase noise in the returned radio signals. Further, the detection unit comprises a processor for processing the refined signals to determine one or more characteristics corresponding to the one or more objects, the processor determining one or more actions based on one or more factors and the one or more characteristics corresponding to the one or more objects. The processor further may determine one or more actions being adoptable by the vehicle based on one or more characteristics that may originate from the RADAR system and/or in conjunction with information originated from another sensor. The vehicle further includes one or more components communicably coupled to the processor for performing the determined one or more actions.

The detection and imaging system may further include a memory for storing information and characteristics corresponding to the one or more objects; and actions performed by the vehicle.

Hereinabove, the at least one ultra-low phase noise frequency synthesizer may be implemented in any manner as described further in the detailed description of this disclosure. Further, the RADAR unit comprises at least one of: traditional single antenna RADAR, dual or multi antenna 5 RADAR, synthetic aperture RADAR, and one or more other RADARs. Further, in an embodiment, the processor may determine phase shift in frequencies of the transmitted radio signals and the returned radio signals. Such phase shift (difference in phase noise frequency) may further be analyzed in light of a frequency of the refined radio signal to self-evaluate overall performance of the detection and imaging system (or specific performance of the ultra-low phase noise frequency synthesizer).

The preceding is a simplified summary to provide an 15 understanding of some aspects of embodiments of the present disclosure. This summary is neither an extensive nor exhaustive overview of the present disclosure and its various embodiments. The summary presents selected concepts of form as an introduction to the more detailed description presented below. As will be appreciated, other embodiments of the present disclosure are possible utilizing, alone or in combination, one or more of the features set forth above or described in detail below.

## BRIEF DESCRIPTION OF THE DRAWINGS

The above and still further features and advantages of embodiments of the present invention will become apparent 30 upon consideration of the following detailed description of embodiments thereof, especially when taken in conjunction with the accompanying drawings, and wherein:

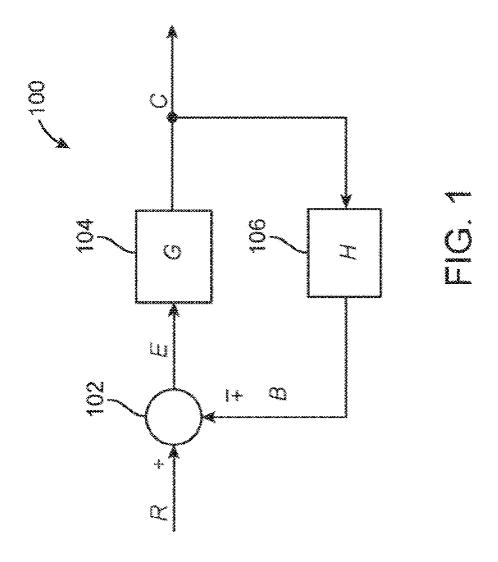

- FIG. 1 illustrates a general block diagram of a negative feedback system;

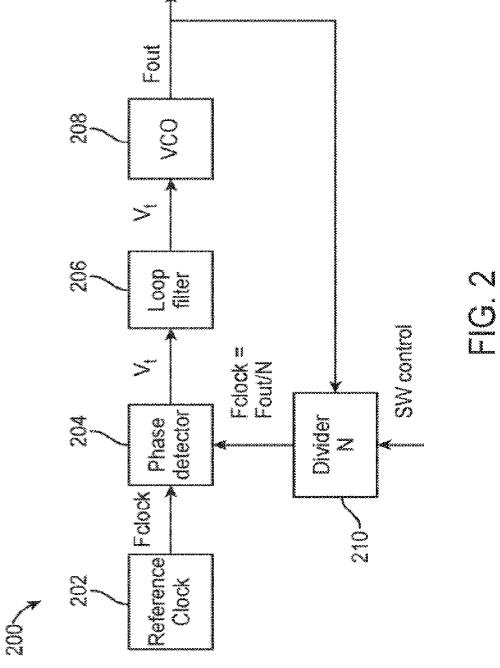

- FIG. 2 illustrates a general block diagram of a standard Phase Lock Loop (PLL);

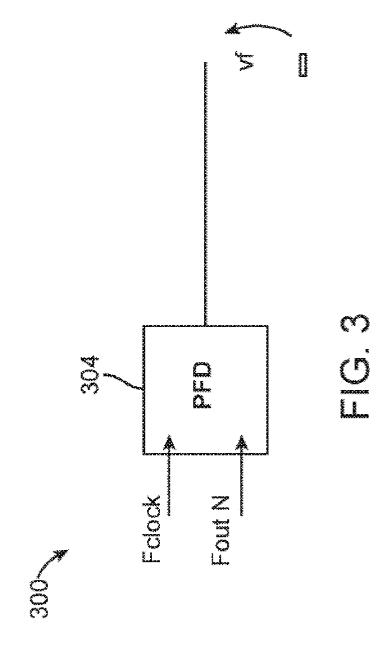

- FIG. 3 illustrates a simplified drawing of a digital phase/ frequency detector;

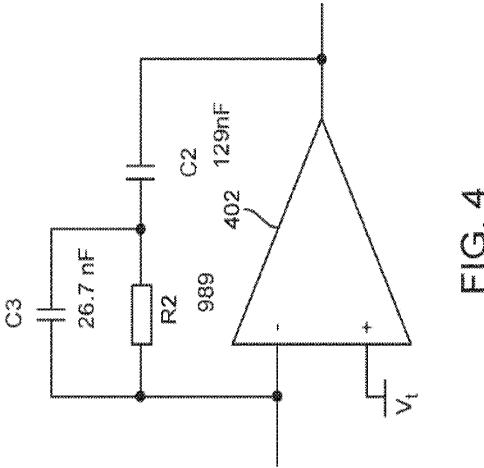

- FIG. 4 illustrates an example of an active filter as applied 40 to a general PLL;

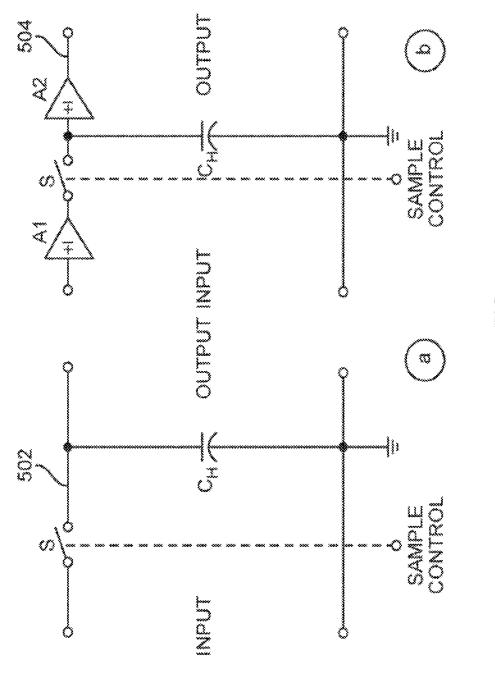

- FIG. 5 illustrates the principle of sample-and-hold mecha-

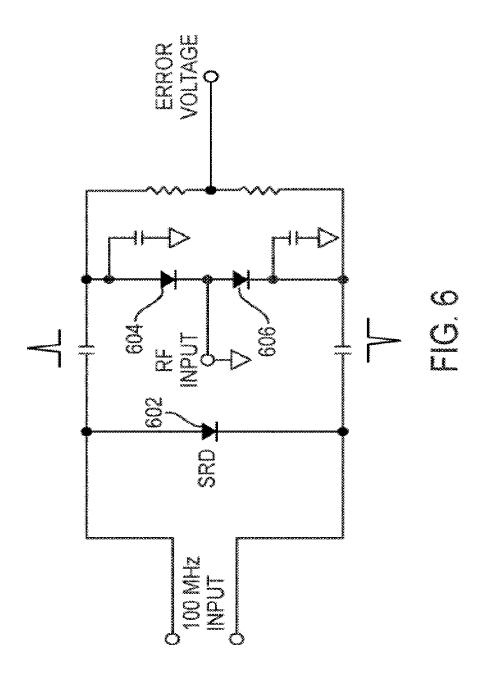

- FIG. 6 illustrates a schematic of the step recovery diode as comb generator feeding the dual schottky diode that acts 45 as phase detector;

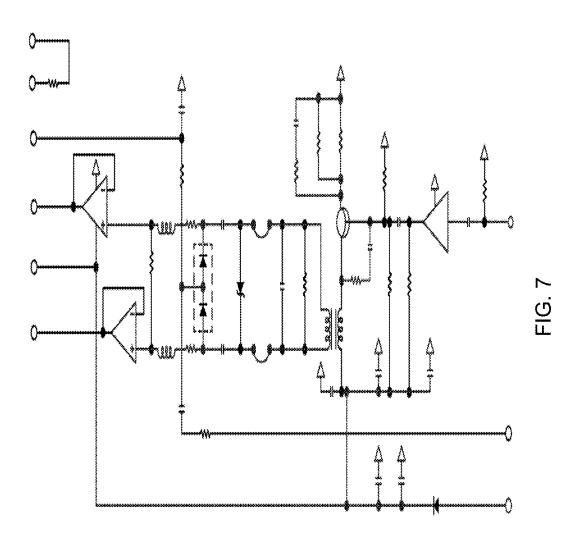

- FIG. 7 illustrates a complete example schematic of the comb generator and sampling phase detector with RF preamplifier and two DC buffers following the phase detector;

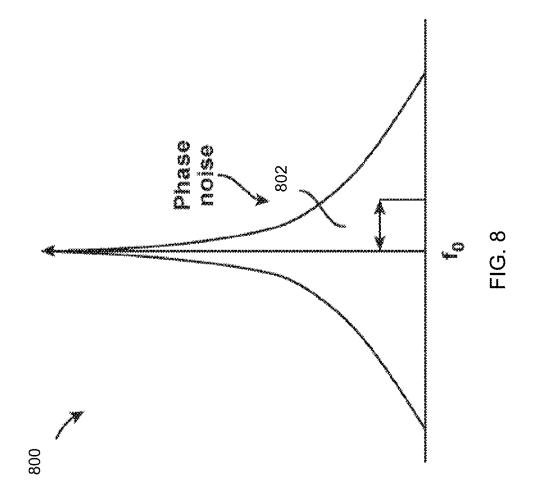

- FIG. 8 illustrates a phase noise plot of an example free 50 running Voltage Control Oscillator (VCO) in the frequency domain (spectrum analyzer), without being locked in a PLL;

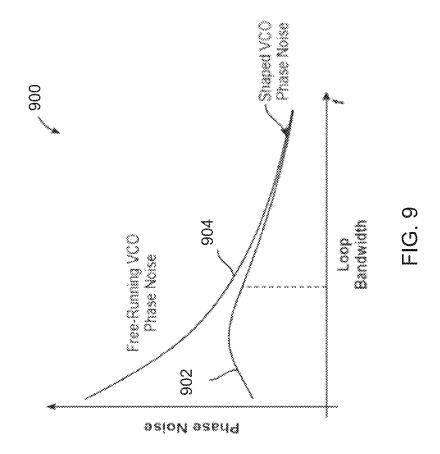

- FIG. 9 illustrates a phase noise plot of an example Voltage Control Oscillator (VCO) in the frequency domain (spectrum analyzer), compensated by being locked in a PLL;

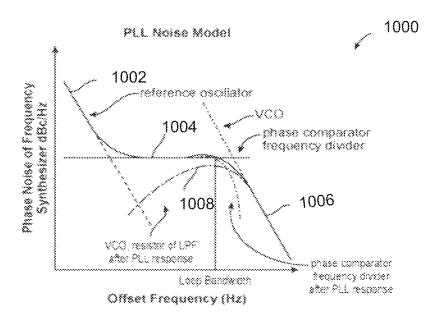

- FIG. 10 illustrates two plots: (a) a simulation of phase noise of an example PLL, and (b) is an actual measurement;

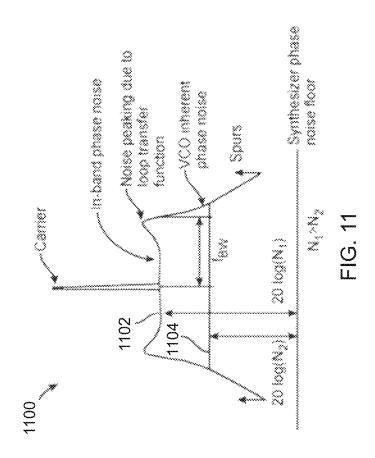

- FIG. 11 illustrates a phase noise plot of a closed loop PLL, showing clearly the effect of the phase detector multiplication number 20\*LOG(N) within loop bandwidth;

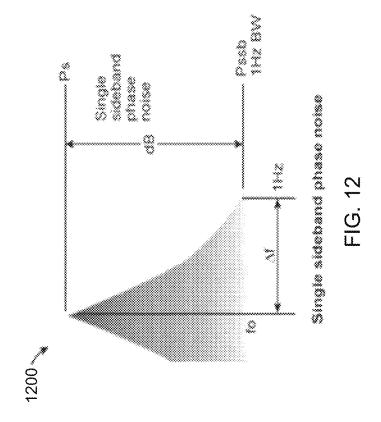

- FIG. 12 illustrates a plot of measurement terms of phase noise in 1 Hz bandwidth at a∆f offset frequency from the carrier.

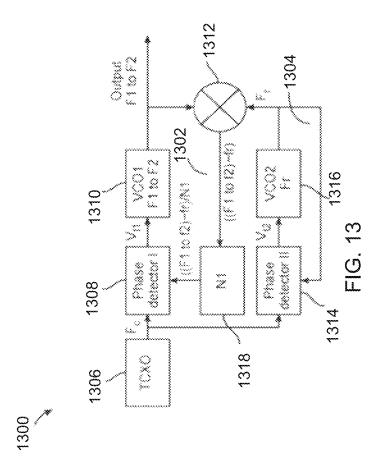

- FIG. 13 illustrates a general block diagram of an example dual loop PLL;

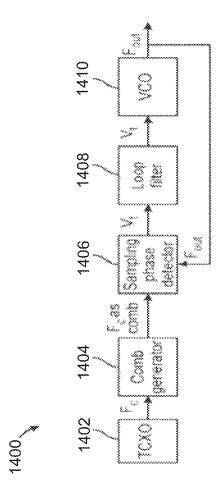

- FIG. 14 illustrates a general block diagram of an example dual sampling PLL;

10

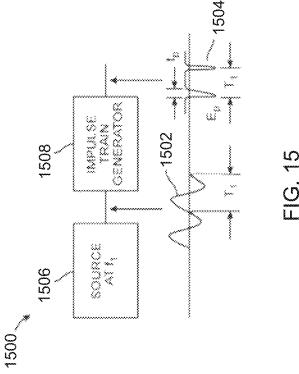

FIG. 15 illustrates how impulse or "comb" generator changes a wave shape of a signal from sine wave to pulses;

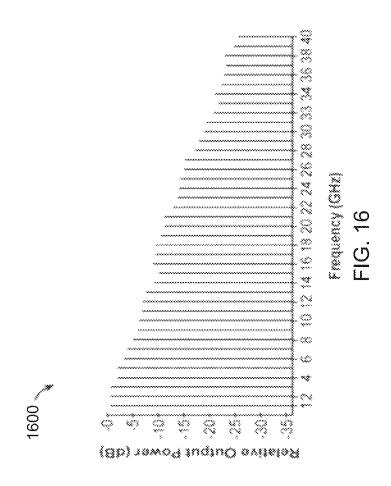

FIG. 16 illustrates an example output of a comb generator in the frequency domain;

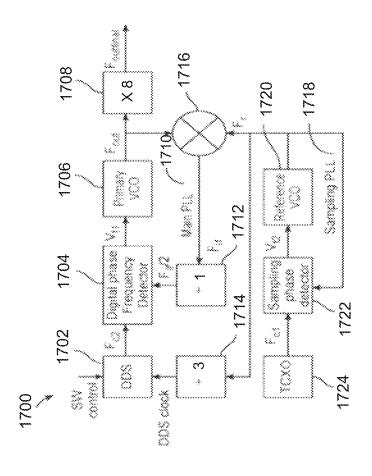

- FIG. 17 illustrates a block diagram of an ultra-low phase noise frequency synthesizer as suggested in a first embodi-

- FIG. 18 illustrates a block diagram of an ultra-low phase noise frequency synthesizer as suggested in a second embodiment;

- FIG. 19 illustrates a block diagram of the sampling PLL system;

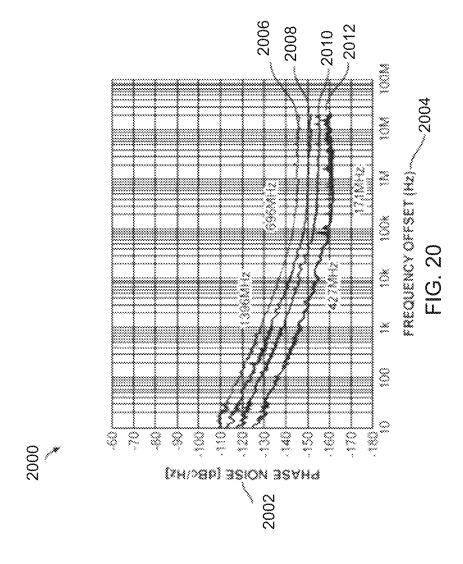

- FIG. 20 illustrates a phase noise simulation plot contributed by a DDS chip in accordance with the first embodiment of the present disclosure;

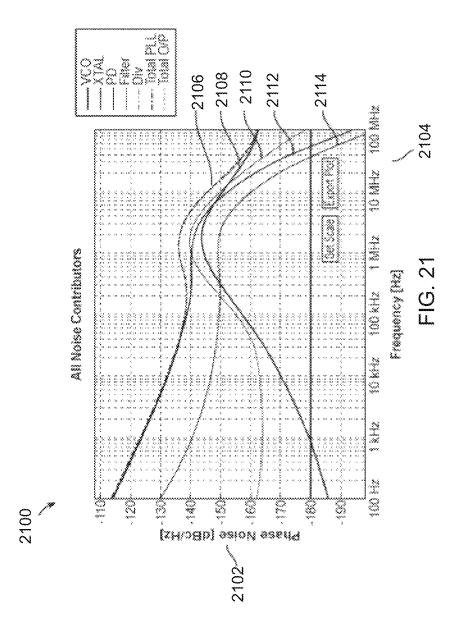

- FIG. 21 illustrates a phase noise simulation plot contributed by a main PLL in accordance with the first embodiment of the present disclosure;

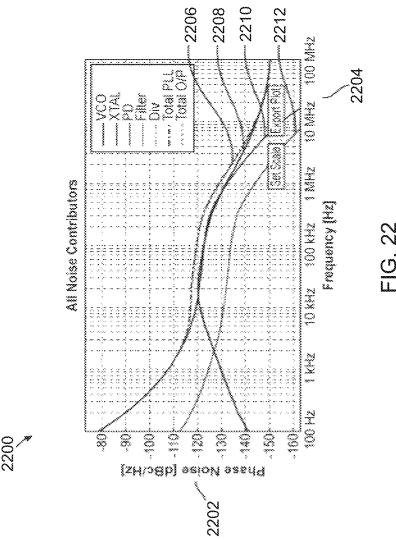

- FIG. 22 illustrates a phase noise simulation plot contribthe embodiments of the present disclosure in a simplified 20 uted by a reference sampling PLL having the TCXO clock (or any other reference Clock) generating input frequencies of 100 MHz in accordance with the first embodiment of the present disclosure:

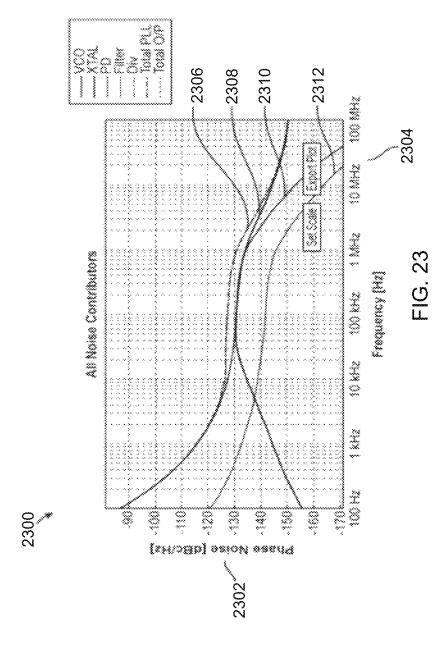

- FIG. 23 illustrates a phase noise simulation plot contrib-25 uted by a reference sampling PLL having the TCXO clock (or any other reference Clock) generating input frequencies of 250 MHz in accordance with the first embodiment of the present disclosure;

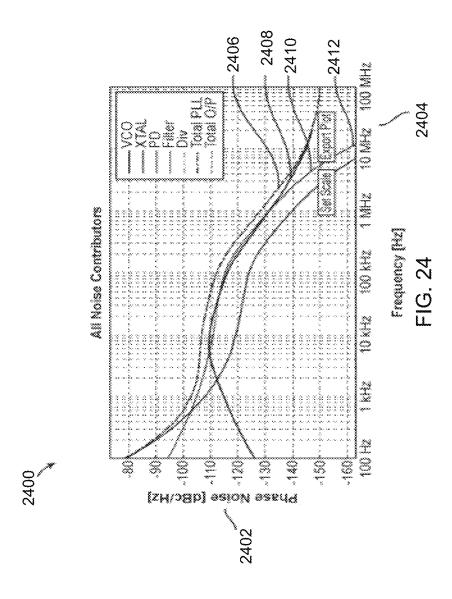

- FIG. 24 illustrates a phase noise simulation plot contributed by a main PLL in accordance with the second embodiment of the present disclosure;

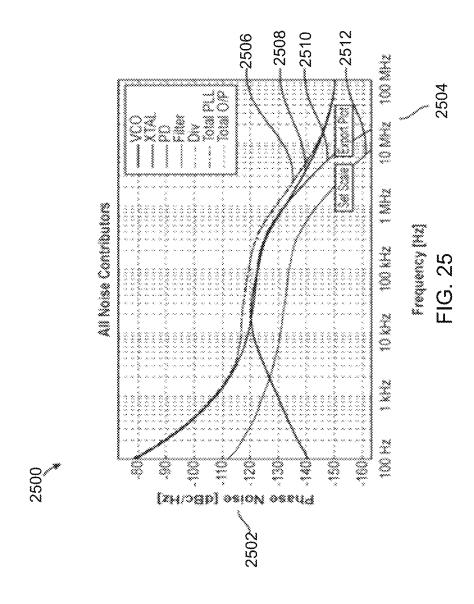

- FIG. 25 illustrates a phase noise simulation plot contributed by a reference sampling PLL having the TCXO clock (or any other reference Clock) generating input frequencies 35 of 100 MHz in accordance with the second embodiment of the present disclosure;

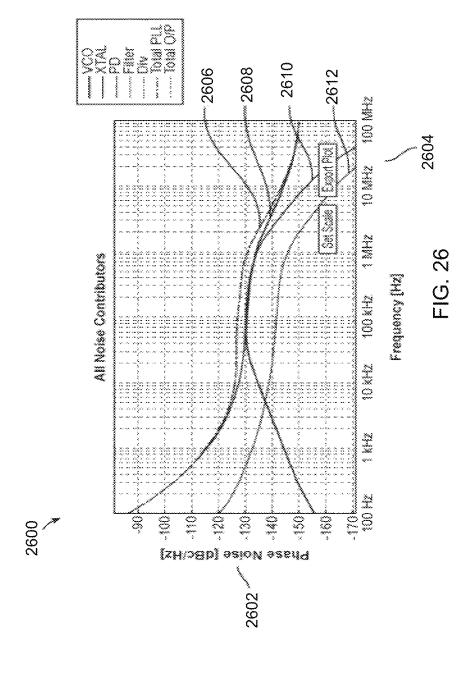

- FIG. 26 illustrates a phase noise simulation plot contributed by a reference sampling PLL having the TCXO clock (or any other reference Clock) generating input frequencies of 250 MHz in accordance with the second embodiment of the present disclosure;

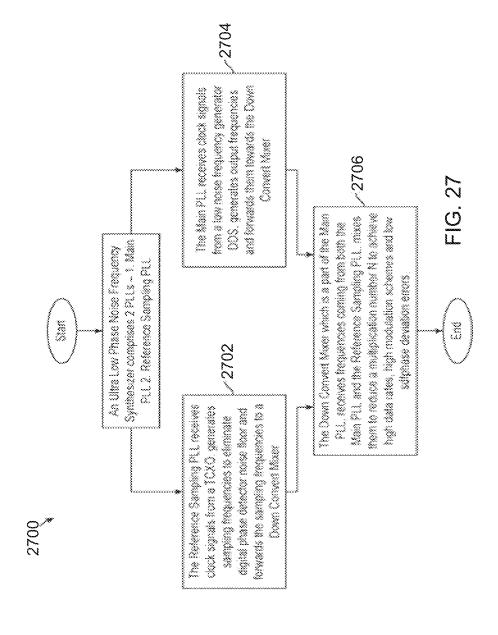

- FIG. 27 illustrates a flow chart depicting the operational method steps of the first embodiment;

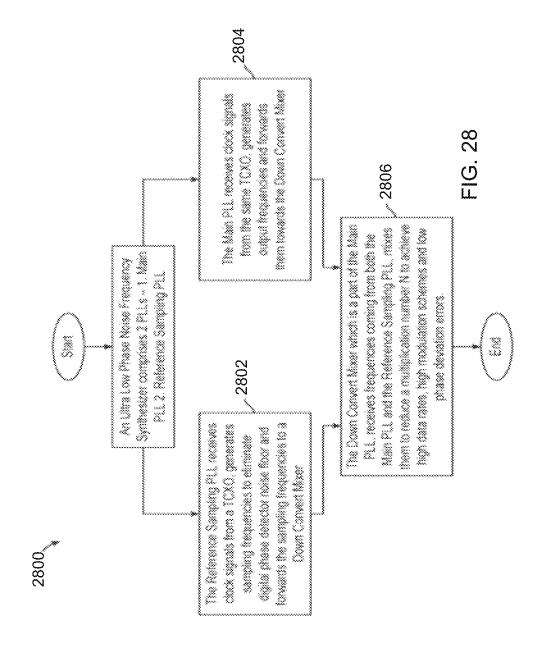

- FIG. 28 illustrates a flow chart depicting the operational method steps of the second embodiment;

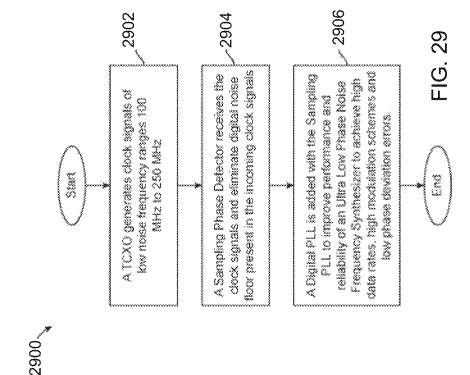

- FIG. 29 illustrates a flow chart depicting the operational method steps of the sampling PLL;

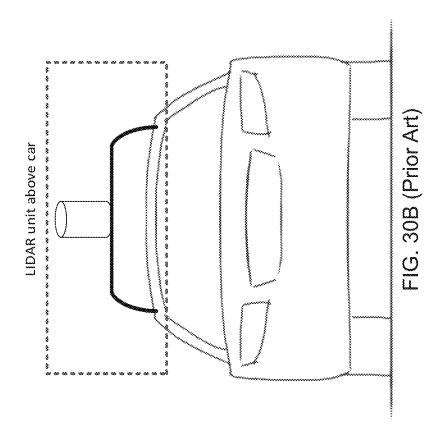

- FIGS. 30A, 30B, 31-36 correspond to prior arts and existing technologies;

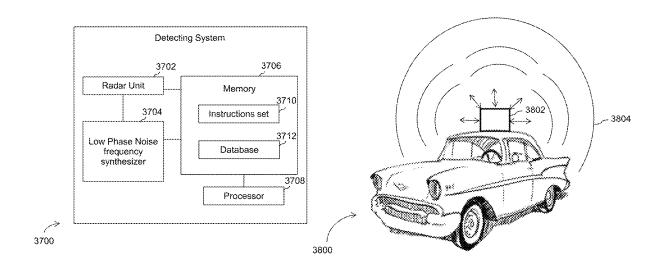

- FIG. 37 illustrates a detection and imaging system, in accordance with various embodiments of the present invention;

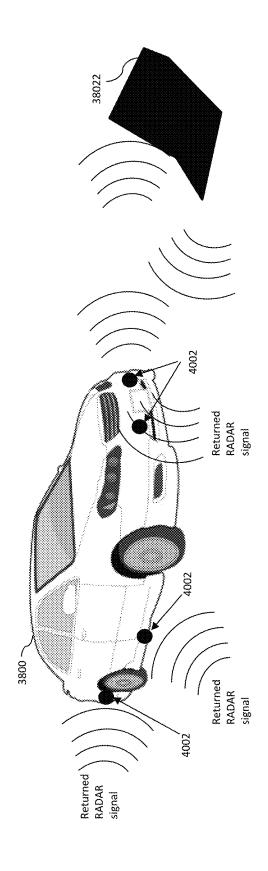

- FIG. 38 illustrates an exemplary vehicle implementing detection and imaging system, in accordance with an 55 embodiment of the present invention;

- FIG. 39 illustrates a block diagram of an exemplary RADAR, in accordance with an embodiment of the inven-

- FIG. 40A illustrates an exemplary 3-dimensional map generation using the RADAR, in accordance with an embodiment of the invention;

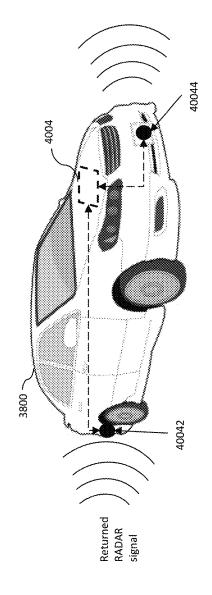

- FIG. 40B illustrates another exemplary 3-dimensional map generation using the RADAR, in accordance with an embodiment of the invention;

- FIG. 41 illustrates another example of 3-dimensional mapping using the RADAR, in accordance with an embodiment of the invention;

FIG. 42 illustrates a flow chat depicting an overall method, in accordance with an embodiment of the invention;

FIG. 43 illustrates a flow chart depicting the operational method steps of first embodiment, in accordance with another embodiment of the invention;

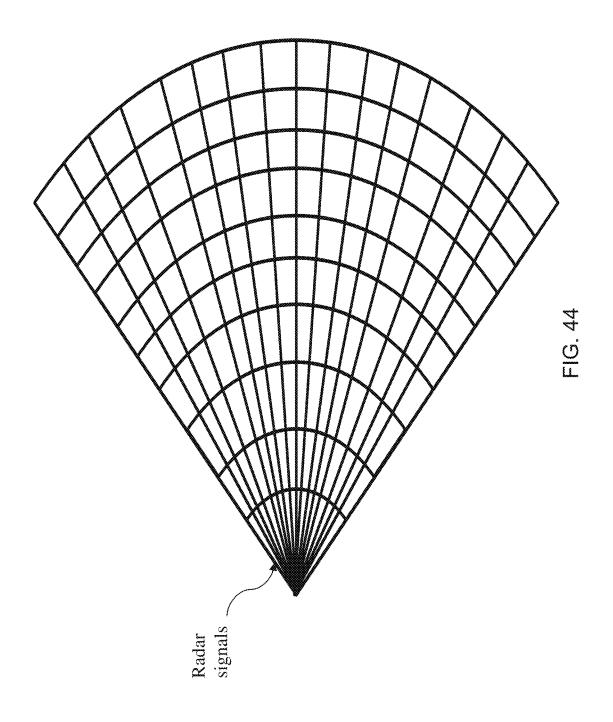

FIG. 44 illustrates a line diagram depicting improvement in RADAR signals, in accordance to the present invention;

FIG. **45** illustrates a line diagram depicting object identification, in accordance with an embodiment of the present invention;

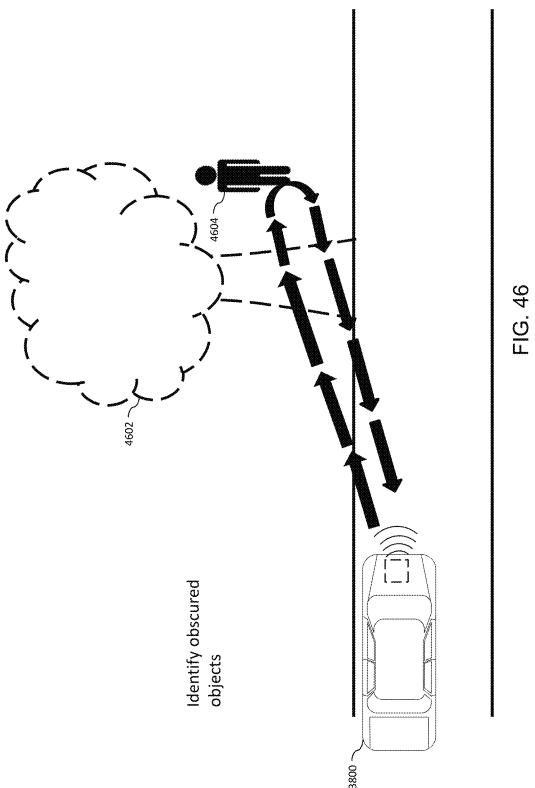

FIG. **46** illustrates a line diagram depicting identification of obscured objects, in accordance with an embodiment of the present invention;

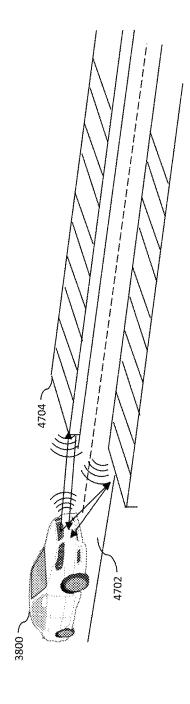

FIG. 47 illustrates a line diagram depicting identification of road and pavement, in accordance with an embodiment of 15 the present invention;

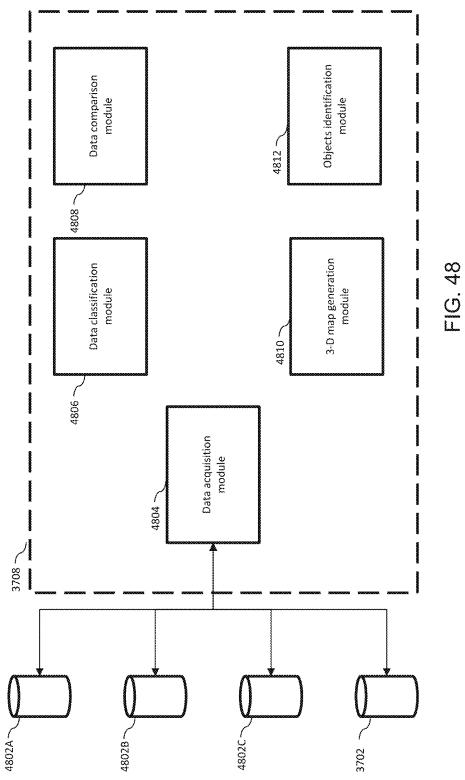

FIG. 48 illustrates a block diagram of a processor, in accordance with an embodiment of the present invention;

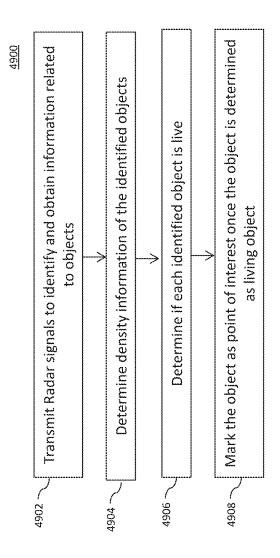

FIG. **49** illustrates a flow chart of a method for identifying live objects using the detection and imaging system, in <sup>20</sup> accordance with an embodiment of the invention.

To facilitate understanding, like reference numerals have been used, where possible, to designate like elements common to the figures.

#### DETAILED DESCRIPTION

As used throughout this application, the word "may" is used in a permissive sense (i.e., meaning having the potential to), rather than the mandatory sense (i.e., meaning must). 30 Similarly, the words "include", "including", and "includes" mean including but not limited to.

The phrases "at least one", "one or more", and "and/or" are open-ended expressions that are both conjunctive and disjunctive in operation. For example, each of the expressions "at least one of A, B and C", "at least one of A, B, or C", "one or more of A, B, and C", "one or more of A, B, or C" and "A, B, and/or C" means A alone, B alone, C alone, A and B together, A and C together, B and C together, or A, B and C together.

The term "a" or "an" entity refers to one or more of that entity. As such, the terms "a" (or "an"), "one or more" and "at least one" can be used interchangeably herein. It is also to be noted that the terms "comprising", "including", and "having" can be used interchangeably.

The term "automatic" and variations thereof, as used herein, refers to any process or operation done without material human input when the process or operation is performed. However, a process or operation can be automatic, even though performance of the process or operation so uses material or immaterial human input, if the input is received before performance of the process or operation. Human input is deemed to be material if such input influences how the process or operation will be performed. Human input that consents to the performance of the process or operation is not deemed to be "material".

The present disclosure includes implementation of an upgraded RADAR unit by incorporating an ultra-low phase noise frequency synthesizer to make the RADAR functioning effective by transmitting radio signals with much lower 60 phase noise than what is found in traditional RADAR systems on the transmit side. On the receive side of the RADAR system the ultra-low phase noise synthesizer adds only a very small amount of phase noise to the signal. More specifically, in an embodiment, the upgraded RADAR unit 65 generates a very low amount of phase noise and thus minimizing the impact of phase noise on the transmitted and

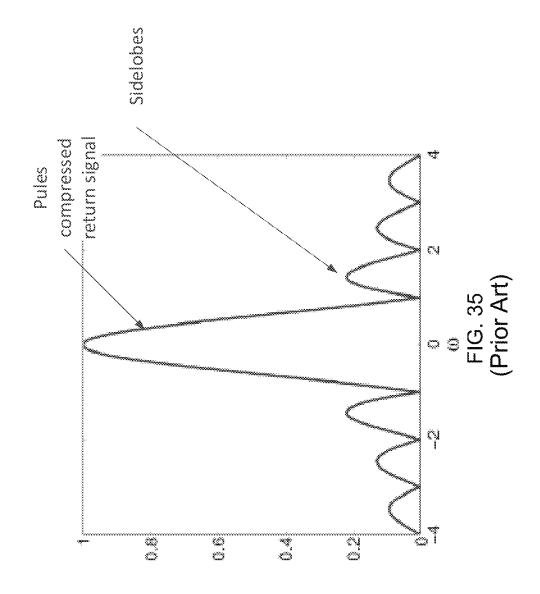

12

the received signal. The RADAR unit may include a Synthetic Aperture RADAR, or any other kind of RADAR, for determining information corresponding to targets. Further, the present disclosure may utilize modulated signal such as Frequency Modulated Continuous Wave (FMCW) of any type or any other modulated signal for the RADAR Unit. As mentioned above FMCW based RADAR are advantageous in terms of power saving Further, in FMCW based RADAR unit, various factors such as distance and velocities may be determined based on frequency differences from the instantaneous transmitted signal rather than travel time. In most cases FMCW RADAR signals are processed with the help of FFT utilizing signal processing windows and pulse compression algorithms. While these methods are good, phase noise of the system still remains important since it is a statistical phenomenon that may be measured and calculated as an average, but instantaneous value thereof cannot be determined, thus it cannot be mitigated easily with existing algorithms. However, its influence on system performance will drastically be reduced with the collaboration of ultralow phase noise frequency synthesizer. As a result, the overall system capability of accuracy and target detection will be vastly improved. Further, once distances, return phases and velocities can be determined with high accuracy, the data can be used to put together an accurate 3 dimensional image of the surroundings.

FIG. 1 illustrates a general block diagram of a negative feedback system 100. The negative feedback system 100 has an input R and an output C, a summer/comparator 102, a forward path function G 104 and a feedback path function H 106. The summer/comparator 102 compares the input R with a sample B of the output C fed back through function H 106, to produce an error signal E that is relative to the difference between the input R and the feedback sample B. This error signal E is fed to the main element G function 104 in the forward path. If the output signal C tends to drift upwards, the error signal E pushes it back downwards and vice versa. Thus, the negative feedback system 100 stabilizes the output signal C. The negative feedback system 100 finds applications in many systems for stabilizing frequency, output power, and many other functions.

FIG. 2 illustrates a general block diagram of a standard Phase Lock Loop (PLL) 200. The PLL 200 is a frequency feedback system comprising a reference clock 202, a digital phase/frequency detector (PFD) 204, a loop filter 206, a Voltage Controlled Oscillator (VCO) 208, and a frequency divider 210.

The VCO 208 is the main output block in the forward path, and is tuned to produce a frequency as set by a tuned circuit. The VCO 208 has a frequency output Fout that can be changed by a control voltage Vt over a pre-set range of frequencies.

The phase detector 204 is a comparator for both the clock input Fclock and the feedback sample from the output Fout divided by divider N 210. The phase detector 204 compares the two input frequencies Fclock and Fout/N. When the two input frequencies are not equal, the device 204 acts as a frequency discriminator and produces either a negative or positive voltage, depending on the polarity of the frequency difference between the two inputs. When the two input frequencies are the device produces an error voltage Vt relative to the phase difference between the two equal frequencies.

The loop filter 206 filters and integrates the error signal produced by the phase detector 204 and feeds it to the VCO 208. The loop filter 206 is usually based on passive com-

ponents like resistors and capacitors, but also in some cases it is a combination of active devices like operational amplifier and passive components.

The reference clock **202** is in general a low frequency crystal oscillator signal source that feeds Fclock to the phase 5 detector **204**, and to which the output signal Fout is "locked". The reference clock **202** is set at some frequency for example a standard frequency 10 MHz. The locking "mechanism" transfers some of the qualities of the reference clock **202** to the main output signal Fout. Its main features 10 usually are: a) frequency stability over temperature—generally in the range of 0.1-5 ppm (parts per million), b) accuracy—Can be tuned to very high accuracy, c) very low phase noise—Its phase noise is transferred to the output signal multiplied by the ratio of **20\*LOG(N)** where N is the 15 ratio between the output frequency and the clock frequency applied to the phase detector **204**.

The frequency divider 210 is based on digital devices like gates and flip-flops, through which the input frequency Fout is divided by a number N to produce Fout/N which is fed to 20 the other input of the phase detector 204. This number N is software controllable. The control signal comes usually from a micro controller or from a PC or from anywhere that basically will send software control to the frequency divider 210 to change the division number N. The target of the 25 division number N is to enable the output frequency of the frequency divider 210 to be equal to the clock frequency of the reference clock 202.

The entire operational procedures of a standard Phase Lock Loop (PLL) 200 is as follows: If an input clock signal 30 Fclock is applied, usually by a reference clock 202, the phase detector 204 compares the phase and frequency of the input signal Fclock with that of the VCO 208 divided by N, and generates an error voltage Vt that is related to the difference in the two signals. The error voltage Vt is then 35 filtered and applied to the control of the VCO 208, thereby varying the VCO 208 frequency in a direction that reduces the frequency difference between the two signals. When the frequencies of the two signals become sufficiently close, the feedback nature of the system causes the system to lock with 40 the incoming signal. Once in lock the VCO 208 frequency divided by N is identical with the input signal Fclock, except for a finite phase difference which is necessary to generate the corrective error voltage Vt to shift the VCO 208 frequency to the input signal frequency Fclock, thus keeping 45 the system in lock.

Any time, the division number N is changed, say for example by 1, the output frequency Fout jumps exactly by a step. In an example, if the reference clock **202** generates a frequency 1 MHz, then every time the division number N 50 changes by steps of 1, the output frequency Fout changes by equal steps of 1 MHz.

Like all negative feedback systems, the PLL **200** has a loop bandwidth set by the component parameters and the loop filter **206**. In other words, the PLL **200** is a sophisticated 55 frequency multiplier with a built-in narrowband, automatically tuned band-pass filter as the output frequency Fout is basically Fclock multiplied by the number N. The loop bandwidth is also responsible directly for how fast the output frequency of PLL **200** may change between different 60 frequencies. The PLL **200** is a device where the VCO **208** is locked to a single clock reference signal which is very low but also very clean and very stable and the output frequency can be changed by equivalent steps by controlling the frequency divider **210** in the feedback loop.

FIG. 3 illustrates a simplified drawing of a digital phase/ frequency detector 204. A phase detector or phase compara14

tor is a frequency mixer, analog multiplier or logic circuit that generates a voltage signal which represents the difference in phase between two signal inputs. It is an essential element of the phase-locked loop (PLL). A specialized variant that additionally detects frequency is referred as Phase Frequency Detector (PFD). A phase-frequency detector is an asynchronous sequential logic circuit which determines which of the two signals has a zero-crossing earlier or more often. When used in a PLL application, lock can be achieved even when it is off frequency. Such a detector has the advantage of producing an output even when the two signals being compared differ not only in phase but in frequency.

The phase/frequency detector 204 compares two input frequencies Fclock and Fout/N. When the two input frequencies are not equal, it acts as a frequency detector and produces one or zeros to produce a voltage control Vt that pushes corresponding VCO 208 in the direction of the reference. In other words, if the VCO 208 is above the reference then the voltage control Vt is high to push the VCO 208 down and vice versa. When the two input frequencies are the same and a frequency lock is achieved, the phase detector 204 acts as a phase detector and compares the two phases, and continues to produce an error voltage to control the frequency and phase of the output device.

FIG. 4 illustrates an example of an active filter as applied to a general PLL 400. The kind of loop filter i.e. passive filter or active filter can be chosen on the basis of specific requirement. A passive loop filter is based on resistors and capacitors only, while an active loop filter is based on an amplifier and a capacitor-resistor network in the feedback system. A passive filter is preferred in cases where, a reference PLL is of a single frequency and will need only a single voltage in order to stay in that single frequency. The other reasons being simplicity, cost and most advantageously no addition of noise, as active devices tend to add additional noise in the system. However, active filters find more acceptances because of the possibility of amplification of the input signal. Amplification is made possible by an operational amplifier employed in the active filter.

The loop filter 206, of FIG. 2, is an active filter that includes an operational amplifier 402 and a capacitor-resistor network 404 in the feedback loop. In some instances, the phase detector 204 of the PLL 200 may produce voltage up to 5 volts but the corresponding VCO 208 may need a voltage of above 5 volts, say, for example, up to 18 volts in order to reach its complete range, so the active filter 206 facilitates not only filtering but also provides the capability to go to higher voltages.

FIG. 5 illustrates the principle of sample-and-hold mechanism 500. The first sample and hold circuit 502 includes a switch S and a hold capacitor CH. The operation of the switch S is controlled by the sample control. When the switch S is closed, a voltage sample of the input frequency is sampled and when the switch is opened, the voltage sample is held on the hold capacitor CH.

The second sample and hold circuit **504** includes two buffers A1 and A2 with unity gain for isolation purposes, in addition to the switch S and the hold capacitor CH. The buffer A2 is preferably an electronic buffer, so that the hold capacitor CH does not discharge parasitically between consecutive samples. In other words, the hold capacitor CH holds the voltage between samples.

FIG. 6 illustrates an example of practical implementation of a comb generator and sampling phase detector. The schematic shows a Step Recovery Diode (SRD) as comb generator feeding the dual schottky diode that acts as phase

detector. The implementation circuit 600 including a Step Recovery Diode (SRD) 602 as a comb generator and the dual schottky diodes 604 and 606 as a phase detector.

The input to the circuit 600 in this example is a clock input of 100 MHz sine wave. The SRD 602 is a special device that 5 turns the 100 MHz sine wave input into a very narrow pulse train of the same frequency, so it acts as a comb generator. The two schottky diodes 604, 606 act as switches and act as sampling switches. The RF voltage (output from corresponding VCO) to be sampled is connected to a point 10 between the two diodes 604 and 606. The SRD 602 creates an output of positive and negative pulses. The positive and negative pulses act as control signals to the diodes 604 and 606 that act like switches. The sampled voltage output is an error DC voltage which is created by sampling the RF input 15 through the dual schottky diodes 604 and 606. The output of the RF signal is sampled whenever the diodes 604 and 606 are opened by the narrow pulses coming from the SRD 602. The voltage sample is held on the capacitors C following the diodes 604 and 606.

FIG. 7 illustrates a schematic of the comb generator and sampling phase detector with a clock pre-amplifier and two DC buffers following the phase detector. The voltage samples are held on two very small capacitors (which are basically the input capacitance of the voltage buffers, no 25 need for external capacitors) on both sides of the dual diode pair, so as not to enable the whole capacitor to discharge parasitically between the samples. These capacitors are buffered by a couple of ultra-low input bias current buffers to prevent discharge between samples. The two voltages are 30 summed, fed to a loop filter, whereby the clean Vt is fed to the VCO to control the frequency.

This implementation of sampling phase detector creates an analog phase detector, very similar to a mixer. The analog sampling phase detector has a certain defined locking space 35 or locking distance, and it does not lock from any frequency difference like the phase/frequency digital detector. It has some locking range and only within that locking range, the VCO locks by itself on the reference. In a sampling PLL, the VCO does not lock on the reference, but on the Nth 40 harmonic of the reference. In other words, one can lock a 9 GHz on the 90th harmonic of the 100 Megahertz clock. This is done as the input frequency is sampled every 100 cycles, not every cycle.

This type of product may contain some "search mechanism" to help lock the PLL. The most common one involves a positive feedback on the loop filter itself. While the loop is not locked, the loop filter acts as a very low frequency oscillator that drives the VCO back and forth across the frequency range. When it passes close enough to the harmonic of the clock, it will lock and stay locked. A nice feature of this mechanism is that it turns off automatically when the loop locks. This happens because of the nature of the loop as a negative feedback system.

However, this type of search mechanism suffers from 55 many problems, its operation is subject to temperature changes and it makes this product difficult to produce, tune and sell successfully.

FIG. 8 illustrates a phase noise plot 800 of an example free running Voltage Control Oscillator (VCO) in the frequency domain (spectrum analyzer), without being locked in a PLL. As said before, Phase noise is a key element in many RF and radio communications systems as it can significantly affect the performance of systems. Phase noise is the frequency domain representation of rapid, short-term, random fluctuations in the phase of a waveform, caused by time domain instabilities also referred to as "jitter".

16

For example, in frequency domain, where the scales are amplitude vs. frequency, ideally a frequency of 100 MHz may look like a single line staying at exactly 100 MHz. However, practically with modern equipment in the laboratory, amplitude vs frequency may not look like a single line but it will look like a single line with a "skirt" 802 which goes wider and wider as we go down. The phase noise plot 800 looks like the skirt 802 on the left and the right of the exact desired frequency  $f_o$ . The quality, height, width of the skirt 802 determines how the phase noise may affect the system or the performance of the system. So, it is desirable to minimize phase noise as much as possible is to improve the system performance.

Phase noise is another term to describe short-term frequency stability. The signal generated by a frequency source is never practically "clean". Its frequency is never absolutely stable at the desired value. It has "Phase Noise" which is frequency shifting, i.e. small frequency shifts at different rates and different amplitudes of the main frequency. It changes around the center set frequency fo at different rates and amplitudes. In time domain, the phase noise may be referred to as jitter. Long term frequency stability is drift of the center frequency over time or over temperature.

FIG. 9 illustrates a phase noise plot 900 of an example Voltage Control Oscillator (VCO) in the frequency domain (spectrum analyzer), compensated by being locked in a PLL.

The upper line 904 is the free running VCO phase noise, before it is locked in a PLL, and the lower line 902 is the shaped VCO phase noise. In the PLL, the principle of locking the VCO to a reference frequency attenuates the phase noise of the VCO, in an amount related to the loop bandwidth. Outside the loop bandwidth, the VCO noise remains almost same as the phase noise without the PLL, while inside loop bandwidth it is attenuated more and more as offset frequency from the main carrier is reduced. At very high frequency, i.e. above the loop bandwidth, the locking almost has no effect, as the phase detector correction signal is not fast enough to reach the VCO for very fast changes or very fast disturbances. However, inside the loop bandwidth or at low frequencies, the compensated phase noise of the VCO is much lower than that of the free running VCO. All the frequencies that is close to the center of the frequency fo are easy to detect and compensate.

FIG. 10 illustrates two plots 1000: (a) a simulation of phase noise of an example PLL, and (b) an actual measurement. FIG. 10 (a) illustrates a simulation graph of phase noise of an example PLL. The simulation graph shows the overall phase noise of the example PLL and includes the contribution of all the components that contribute to the phase noise. The simulation graph illustrates first, second and third regions 1002, 1004 and 1006 of the phase noise. The first region 1002 which is very close to the carrier depicts a steep line which basically comes from the reference clock such as the Temperature Controlled Crystal Oscillator (TCXO, or any other reference clock device). The first region depicts the noise of the TCXO, multiplied by 20 log N, where N is the ratio of output frequency to the clock frequency. The second region 1004 depicts a flat phase noise which is basically the noise floor of the digital phase detector multiplied by the same ratio of 20 log N. The third region 1006 depicts a steep line which is the inherent VCO phase noise not affected by the loop bandwidth and locking phenomenon. The dashed line 1008 depicts the VCO "corrected" phase noise inside loop bandwidth. Below the flat area, the compensated VCO phase noise does not affect the overall result because it is way below the noise floor of the phase detector multiplied by that ratio. The actual measure-

ment of phase noise of an example PLL is illustrated in FIG.  $10\ (b)$ . One can see clearly the similarity between the two curves.

FIG. 10 illustrates a phase noise plot 1100 of a closed loop PLL, showing clearly the effect of the phase detector multiplication number 20\*LOG(N) within loop bandwidth. The phase noise plot 800 illustrates phase noises on both sides of the carrier frequency fo, where the left side is a mirrored image of the right side. The phase noises on both sides of the carrier fo looks like it is passing through a band-pass filter.

As illustrated, on both sides, the in-band phase noise inside the loop bandwidth is flat in shape and is equal to the phase detector and/or the reference clock noise multiplied by 20 log N. At the point of the loop bandwidth, the phase noise goes up before going down again. This is due to addition of 3 dB due to a combination of phase noise of the free running VCO and the phase detector. The upper straight line 1102 depicts a phase noise contributed by the phase detector at N1 and the lower straight line 1104 depicts a phase noise contributed by the phase detector at N2. It can be seen that, there is difference in phase noise in the flat area, due to two different "N" numbers. The phase detector contributes a higher in-band phase noise at a higher value of N.

Thus, in order to achieve low phase noise, it is essential to: a) choose components such as phase detector and reference clock with the lowest inherent phase noise possible, and b) lower the ratio number N as much as possible.

FIG. 11 illustrates plot 12902200 of measurement terms of phase noise in 1 Hz bandwidth at a  $\Delta f$  offset frequency from the carrier. The phase noise expression is usually in dBc, i.e. dB relative to the carrier c power level Ps, in other words how low it is compared to the carrier per Hz, in a bandwidth of 1 Hz. That is basically the term that is used for phase noise, dBc per Hertz (dBc/Hz) at a certain  $\Delta f$  from the carrier.

As an example for the measurement method, suppose  $\Delta F$  is 10 KHz, the phase noise power level Pss is measured at the level of –70 dBm on the spectrum analyzer, and the carrier power level Ps is measured at the level of 10 dBm, the ratio between the Ps 10 dBm and the PssB –70 dBm at 10 KHz from the carrier is therefore 80 dB, so the phase noise at 10 KHz offset from carrier and is –80 dBc/Hz.

For many systems, the important parameter to evaluate performance is not the phase noise measured at a single frequency offset from the carrier, but the integrated phase noise from one offset frequency to another one. Following are four different equations and terms to define integrated phase noise:

$$\int L(f)df$$

$$S_{phi}(f) = \left(\frac{180}{\pi}\right) \cdot \sqrt{2 \cdot \int L(f)df}$$

$$S_{nu}(f) = \sqrt{2 \cdot \int L(f) \cdot f^2 df}$$

$$S_y(f) = \left(\frac{s_{nu}(f)}{f_{osc}}\right)$$

Where the first equation describes single sideband phase noise [dBc]

The  $2^{nd}$  equation describes the spectral density of phase modulation, also known as RMS phase error (degrees) The  $3^{rd}$  equation describes the spectral density of frequency 65 fluctuations, also known as RMS frequency error or residual

FM (Hz)

18

The 4<sup>th</sup> equation describes the spectral density of fractional frequency fluctuations

For example, the first equation defines the Phase Noise in dBc. It can be translated by the 2nd equation to degrees (relevant in respect of learning modulation schemes). As per further equations, the phase noise can also be translated in terms of Hz and time domain phase jitter seconds.

FIG. 13 illustrates a general block diagram 1300 of an example dual loop PLL. The main target of the dual loop design is to reduce the multiplication number N in the main PLL.

The dual loop PLL 1300 includes an upper PLL 1302, referred to as a main PLL 1302, and a lower PLL 1304, referred to as a reference PLL 1304, a TCXO 1306 operating as a master clock, feeding a clock signal Fc to both the primary PLL 1302 and the reference PLL 1304.

The reference PLL 1304 includes a first phase detector 1314, and a single frequency first VCO 1316 that operates at a reference frequency Fr. The reference frequency Fris fed to a first input of a down convert mixer 1312.

The main PLL 1302 includes a second phase detector 1308 and a second VCO 1310 that generates an output frequency range F1 to F2. A sample of the output frequency range F1 to F2 is fed to the second input of the down convert mixer 1312 and mixed with a single reference frequency Fr. The output from the down convert mixer 1312 is at a much lower frequency (F1 to F2)-Fr. This lowered frequency is fed back to the second phase detector 1308 through a frequency divider 1318 of value N1.

Therefore: a) Without the down convert mixer **1412**: F1 to  $F2=N\times Fc$ , b) With the down convert mixer **1312**: (F1 to  $F2)-Fr=N1\times Fc$ . As a result there is a reduction in the number N: N1/N=((F1 to F2)-Fr)/(F1 to F2).

The N1 number is basically the division number that the frequency divider 1318 will use to divide the output of the mixer 1312 and feed to the second phase detector 1308. The value of N1 is set as minimal, as the output from the mixer 1312 is at a much lower frequency than original frequency range F1 to F2.

To give an example: a) Suppose Fc=1 MHz, b) Suppose F1 to F2=10,000 to 11,000 MHz. Then N=10,000 to 11,000. Now If Fr=9000 MHz, then ((F1-F2)-Fr)=1000 to 1900 MHz. Then N1=1000 to 1900. Thus, the value of N is reduced from 11,000 to 1900. In dB, it is a ratio of 15 dB. This means, that the phase noise is reduced by a factor of 15 dB.

The disadvantage of the example dual loop design is that while nicely reducing the number N in the main PLL, the reference PLL, containing a digital phase/frequency detector becomes the main factor contributing to the overall output phase noise.

FIG. 14 illustrates a general block diagram 1400 of an example sampling PLL. The sampling PLL 1400 includes a TCXO 1402, a comb generator 1404, a sampling phase detector 1406, a loop filter 1408, and a VCO 1410. The sampling PLL 1400 does not include digital phase/frequency detector and frequency divider. Thus, no digital noise floor is generated that can be multiplied and affect performance of the system.

The TCXO **1402** feeds the clock signal Fclock to the comb generator **1404**. The comb generator **1404** is a device that changes the input sine wave signal at frequency Fclock to an output signal of very narrow pulses at the same frequency as the input sine wave signal.

The pulse output from the comb generator **1404** is used as a control signal to the sampling phase detector **1406**. The sampling phase detector **1406** receives an RF signal of

frequency Fout from the VCO 1410, and includes two diodes acting as switches to sample the RF signal by opening and closing the diodes based on the narrow pulses from the comb generator 1404. The sampled voltage Vt produced is "held" on capacitors and buffered until the next sample period. The voltage samples are always at the same level, thus a DC voltage Vt is generated by the sampling phase detector 1406. The loop filter 1408 cleans and filters the DC voltage Vt, and provides it to the VCO 1410 to control the VCO frequency Fout. Fout=Fclock\*N, where N is the Nth spectral harmonic line in the "comb" spectrum.

FIG. 15 illustrates block diagram 1500 depicts how the impulse or "comb" generator 1404 changes a wave shape of a signal from sine wave 1502 to narrow pulses 1504. A frequency source 1506 generates the input sine wave 1502 of frequency F1 and time period T1.

The comb generator **1404** turns the input sine wave **1502** to a series of very narrow pulses **1504** with same time period T1, and a pulse bandwidth as tp in the time domain. For 20 example, if the frequency of input sine wave **1502** is 100 MHz, then the impulse train generator **1508** generates a series of very sharp narrow pulses **1504** of the same frequency.

FIG. 16 illustrates an example output 1600 of a comb 25 generator 1404 in the frequency domain. In the frequency domain (spectrum analyzer screen), the output 1600 of the comb generator 1404 looks like a "comb", i.e. a row of lines extending up to very high frequency. In theory, if the bandwidth of the clock pulse is infinitesimal, the row of lines appear with equal amplitude to infinity. The output 1600 looks like a series of lines, with the spacing between the lines same as the initial frequency. In an example, if the initial frequency is 1 GHz, the spectrum of lines is 1 GHz apart.

FIG. 17 illustrates a block diagram 1700 of an ultra-low phase noise frequency synthesizer as suggested in a first embodiment. The ultra-low phase noise frequency synthesizer 1700 includes two Phase Lock Loops (PLLs). One is a main PLL **1710** and the other one is a reference PLL **1718**. 40 The main PLL 1710 comprises of a high frequency low noise Direct Digital Synthesizer (DDS) 1702 to generate at least one clock signal Fc2 of variable frequency range. The high frequency low noise DDS 1702 generates the at least one clock signal Fc2 of variable frequency range by taking 45 input from at least one software controllable instructions and at least one DDS clock signal. The frequency of the at least one clock signal Fc2 is always lower than the frequency of the at least one DDS clock signal. The at least one DDS clock signal is generated by a first fixed frequency divider 50 1714. The high frequency low noise DDS 1702 forwards the generated at least one clock signal Fc2 of variable frequency range towards a Digital Phase Frequency Detector 1704.

The Digital Phase Frequency Detector 1704 compares two signals coming from two directions and generates at 55 least one signal. One signal is the at least one clock signal Fc2 of variable frequency range generated by the high frequency low noise DDS 1702. The second signal is at least one signal of frequency Fif/N1 generated by a second fixed frequency divider 1712. The Digital Phase Frequency 60 Detector 1704 compares these two signals and generates at least one first control voltage Vt1 and forwards it towards a primary Voltage Control Oscillator (VCO) 1706. The primary Voltage Control Oscillator (VCO) 1706 generates at least one output signal of frequency Fout from the received 65 at least one first control voltage Vt1. The main PLL 1710 further comprises a down convert mixer 1716.

20

The primary role of the reference PLL 1718 is to help the main PLL 1710 in reducing the phase noise present in the at least one output signal Fout. The reference PLL 1718 comprises a reference clock (for example a Temperature Compensated Crystal Oscillator (TCXO)) 1724 to generate at least one first clock signal of a fixed single frequency Fc1. Further, the reference PPL comprises a sampling phase detector 1722 (that includes the comb generator and the sampling phase detector) to generate at least one second control voltage Vt2 and a reference Voltage Control Oscillator (VCO) 1720.

One important thing to notice here is that unlike other dual loop designs, the reference PLL 1718 uses the sampling phase detector 1722. The reference PLL 1718 does not use any kind digital devices like the Digital Phase Frequency Detector 1704, or the first fixed frequency divider N1 1714. Simultaneously the reference clock 1724 present in the sampling PLL 1718 is also a very low noise generating device. Due to these reasons the contribution of phase noise from the reference PLL 1718 to the main PLL 1710 becomes close to negligible. The reference Voltage Control Oscillator (VCO) 1720 generates at least one reference signal Fr and forwards it towards the down convert mixer 1716. The reference PLL 1718 plays a major part in all relevant communications and similar systems by being part of various frequency synthesizers, and also as a standalone frequency source for all the systems of up and down conversion processes in the same equipment.

The down convert mixer 1716 receives at least one reference signal of frequencies Fr and at least one output signal of frequency Fout and generates at least one intermediate signal of frequency Fif and forwards it towards a second fixed frequency divider 1712. The second fixed frequency divider 1712 generates at least one signal of frequencies Fif/N1 by dividing the incoming at least one signal of frequency Fif by a predefined factor. The second fixed frequency divider 1712 forwards the generated at least one signal of frequencies Fif/N1 towards the Digital Phase Frequency Detector 1704. The primary VCO 1706 forwards the at least one output signal Fout towards a fixed frequency multiplier 1708 to generate at least one final output signal Fout final.

It is important to notice that frequency divider **1712** is optional and the main PLL can operate without division of Fif.

To explain the above disclosed disclosures with an example let's say the reference clock 1724 generates the at least one first clock signal of a fixed single frequency Fc1 100 MHz. The sampling phase detector 1722 generates the second control voltage Vt2 by sampling the at least one first clock signal of a fixed single frequency Fc1 100 MHz and forwards the sampled values of the at least one first clock signal of a fixed single frequency Fc1 100 MHz towards the reference Voltage Control Oscillator (VCO) 1720. The reference Voltage Control Oscillator (VCO) 1720 generates the at least one reference signal Fr and forwards it towards the down convert mixer 1716. In an example, the reference VCO 1720 generates frequency of 9.4 GHz.

In the example, the first frequency divider 1714 divides the generated reference signal of frequency 9.4 GHz by a predefined factor of 3 to generate the at least one DDS clock signal. The high frequency low noise DDS 1702 receives the at least one DDS clock signal, and based on the at least one software controllable instructions, generates the at least one clock signal Fc2 of variable frequency range from 0.1 GHz to 0.225 GHz.